ADSP-214xx SHARC Processor Hardware Reference A-179

Registers Reference

Parallel Data Acquisition Port Control Register

(IDP_PP_CTL)

The

IDP_PP_CTL register (shown in Figure A-96 and described in

Table A-93) provides 20 mask bits that allow the input from any of the 20

pins to be ignored.

For more information on the operation of the parallel data acquisition

port, see Chapter 11, Input Data Port. For information on the pin mux-

ing that is used in conjunction with this module, see “Pin Multiplexing”

on page 23-28.

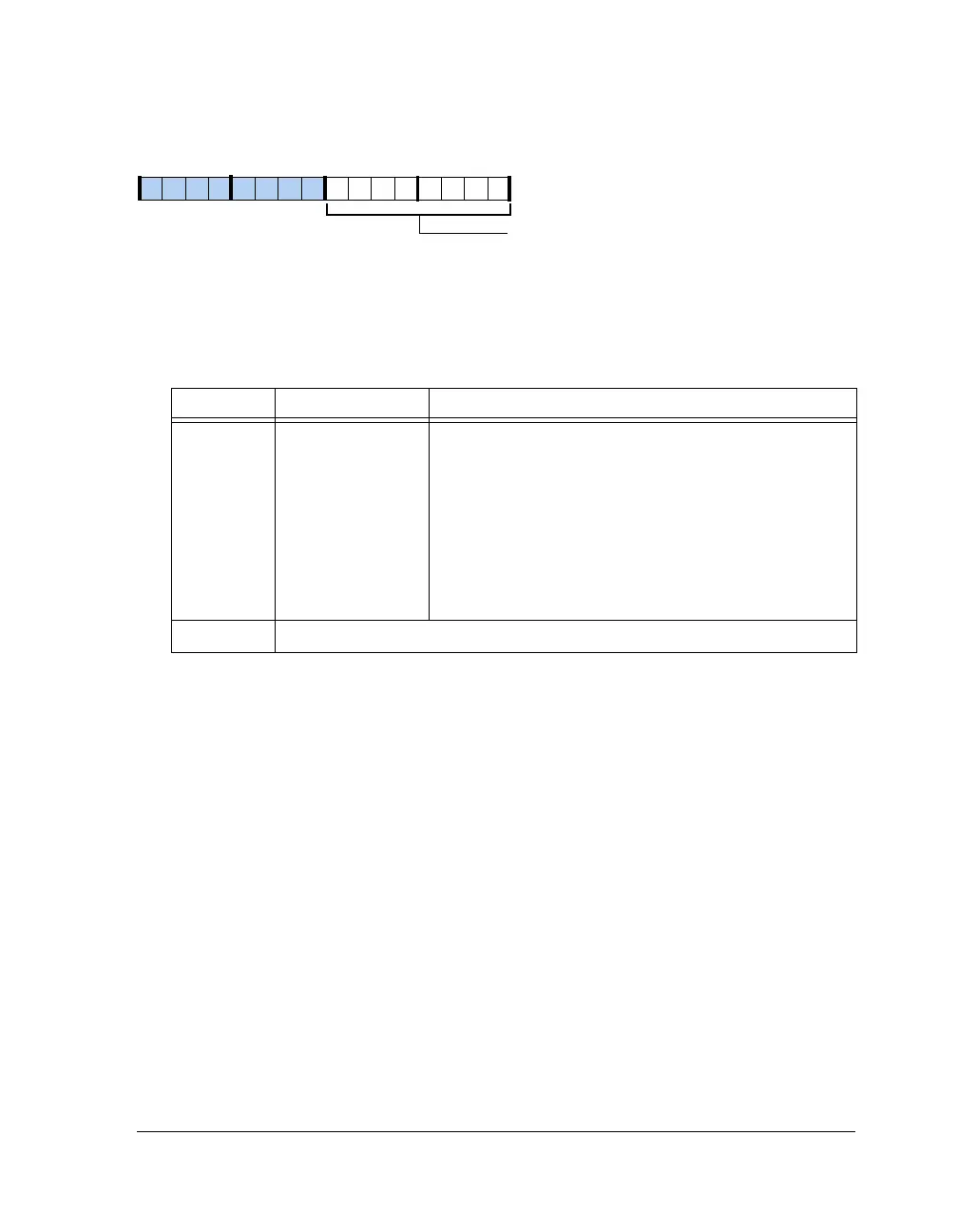

Figure A-95. IDP_CTL2 Register

Table A-92. IDP_CTL2 Register Bit Descriptions (RW)

Bit Name Description

7–0 FAEx First Active Edge for Channel x.

1= nth IDP channel starts shifting in data from the first ris-

ing edge of LRCLK after IDP is enabled. This data is

latched after the next falling edge of LRCLK.

0 = nth IDP channel starts shifting in data from the first

falling edge of LRCLK after IDP is enabled. This data is

latched after the next rising edge of LRCLK. Reset value of

all these bits is 0. These bits are used only if IDP_INTEN

bit (IDP_CTL1[24]) is set.

8–31 Reserved

FAEx (7–0)

First Active Edge for

Channel x

09 837564 2114 12 11 101315

Loading...

Loading...