TCB Storage

2-16 ADSP-214xx SHARC Processor Hardware Reference

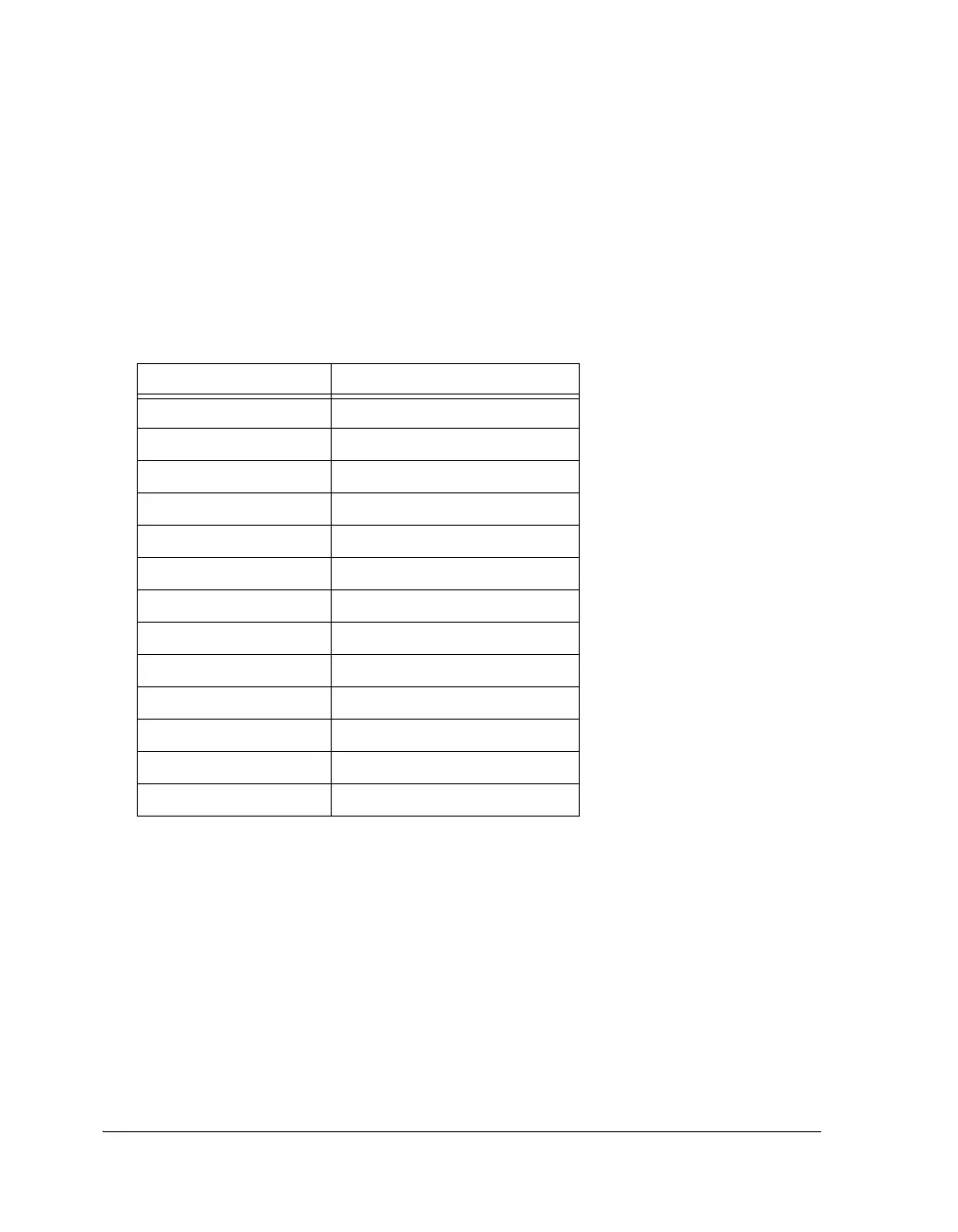

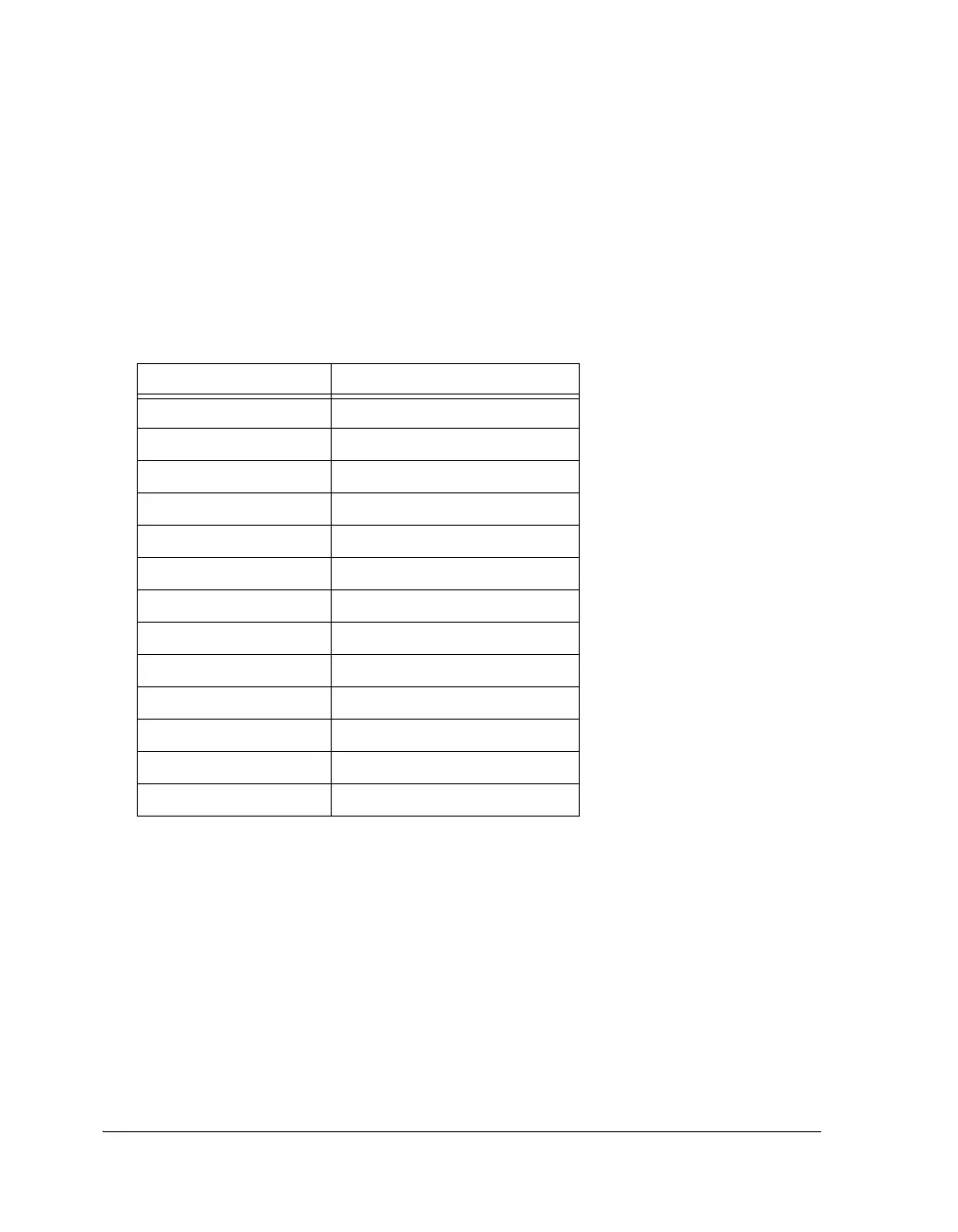

FIR Accelerator TCB

The FIR accelerator DMA supports circular buffer chained DMA.

Table 2-18 shows the required TCBs for chained DMA. The FIR acceler-

ator does not support circular buffering for the coefficient buffer.

The CCFIR register is loaded with the values in the CCFIR TCB field

and is decremented from that value onwards. However, coefficient

loading continues until the number of coefficients, equal to the tap

length, are read. This is true even if the CCFIR register reaches zero

as in the case of a tap length = 10, and the

CCFIR field in the TCB is

initialized to 0. The value in the

CCFIR register is –10 after all coef-

ficients are loaded.

Table 2-18. FIR TCBs

Address Register

CP[18:0] CPFIR

CP[18:0] + 0x1 CCFIR

CP[18:0] + 0x2 CMFIR

CP[18:0] + 0x3 CIFIR

CP[18:0] + 0x4 OBFIR

CP[18:0] + 0x5 OCFIR

CP[18:0] + 0x6 OMFIR

CP[18:0] + 0x7 OIFIR

CP[18:0] + 0x8 IBFIR

CP[18:0] + 0x9 ICFIR

CP[18:0] + 0xA IMFIR

CP[18:0] + 0xB IIFIR

CP[18:0] + 0xC FIRCTL2

Loading...

Loading...