ADSP-214xx SHARC Processor Hardware Reference 16-7

Peripheral Timers

When clocked internally, the clock source is the processor’s peripheral

clock (

PCLK). The timer produces a waveform with a period equal to 2 x

TMxPRD and a width equal to 2 × TMxW. The period and width are set

through the TMxPRD30–0 and the TMxW30–0 bits. Bit 31 is ignored for both.

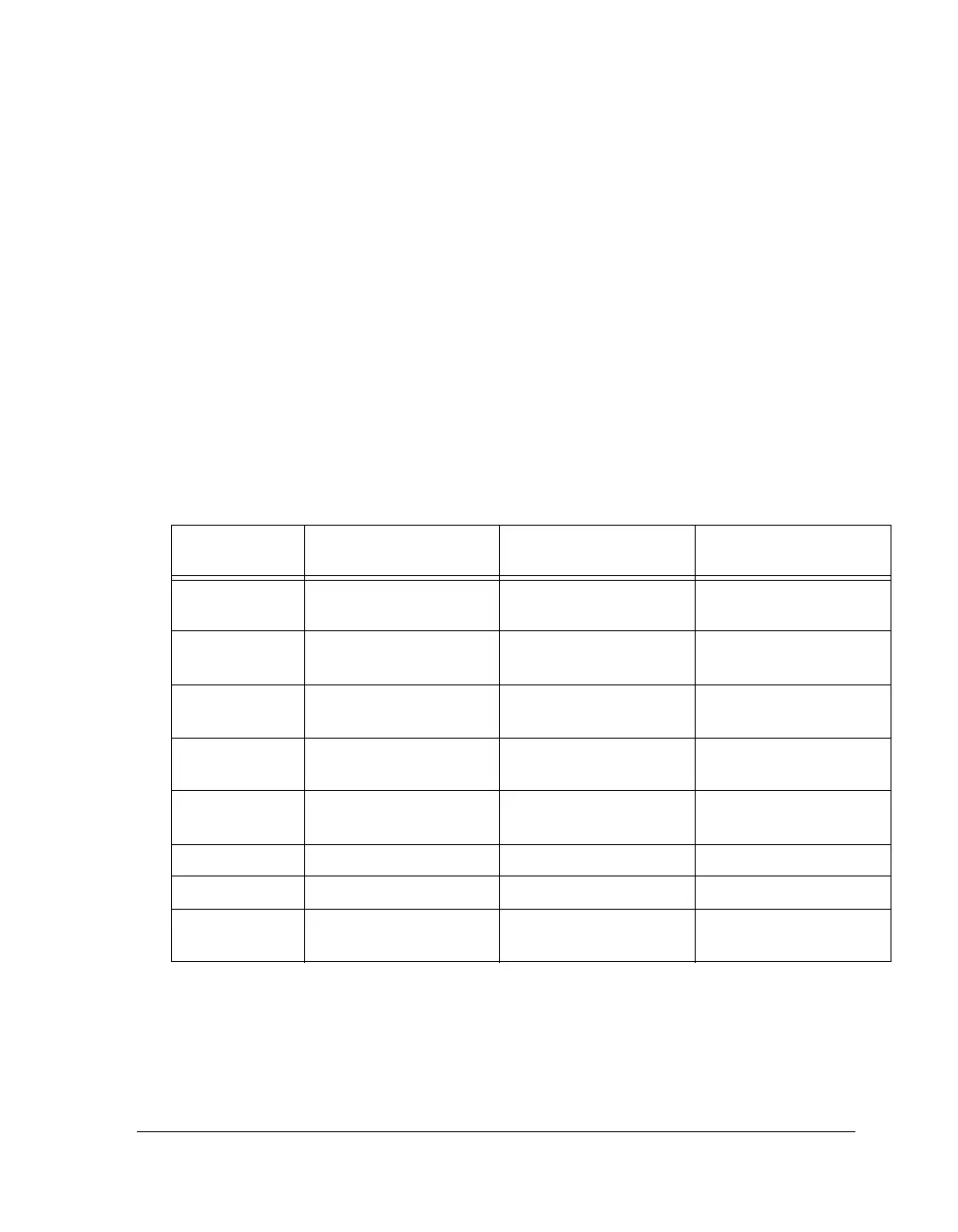

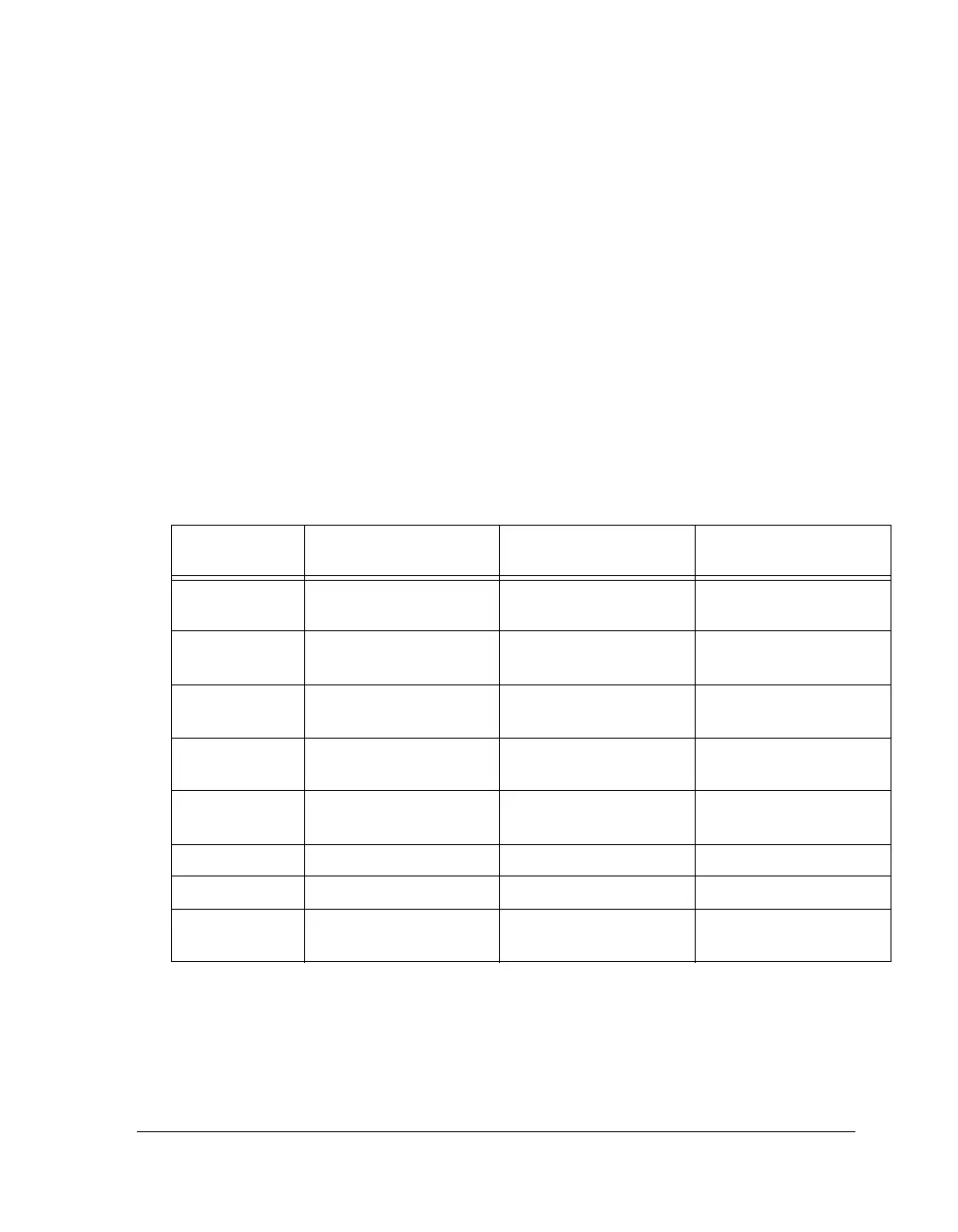

Operating Modes

The three operating modes of the peripheral timer; PWM_OUT,

WDTH_CAP, and EXT_CLK, are described in Table 16-4 and the fol-

lowing sections.

Table 16-4. Timer Signal Use

Register

Settings

PWM_OUT Mode WIDTH_CAP Mode EXT_CLK Mode

MODE 01 = Output PWM Wave-

form

10 = Input Waveform 11 = Input Event

TIMEN 1 = Enable & Start Timer

0 = Disable Timer

1 = Enable & Start Timer

0 = Disable Timer

1 = Enable & Start Timer

0 = Disable Timer

PULSE 1 = Generate High Width

0 = Generate Low Width

1 = Measure High Width

0 = Measure Low Width

1 = Count at event rise

0 = Count at event fall

PRDCNT 1 = Generate PWM

0 = Single Width Pulse

1 = Measure Period

0 = Measure Width

Unused

IRQEN 1 = Enable Interrupt

0 = Disable Interrupt

1 = Enable Interrupt

0 = Disable Interrupt

1 = Enable Interrupt

0 = Disable Interrupt

Period WO: Period Value RO: Period Value WO: Period Value

Width WO: Width Value RO: Width Value Unused

Counter RO: Only if not enabled

Counts down on PCLK

RO: Only if not enabled

Counts up on PCLK

RO: Only if not enabled

Counts down on Event

Loading...

Loading...