Features

13-2 ADSP-214xx SHARC Processor Hardware Reference

Features

The S/PDIF interface has the following features.

• AES3-compliant S/PDIF transmitter and receiver.

• Transmitting a biphase mark encoded signal that may contain any

number of audio channels (compressed or linear PCM) or

non-audio data.

• S/PDIF receiver managing clock recovery with separate S/PDIF

PLL or optional using external PLL circuit.

• S/PDIF receiver direct supports DTS frames of 256, 512, 1024,

2048, and 4096 (4096 frames are not supported for the

ADSP-2146x processors).

• Managing user status information and providing error-handling

capabilities in both the transmitter and receiver.

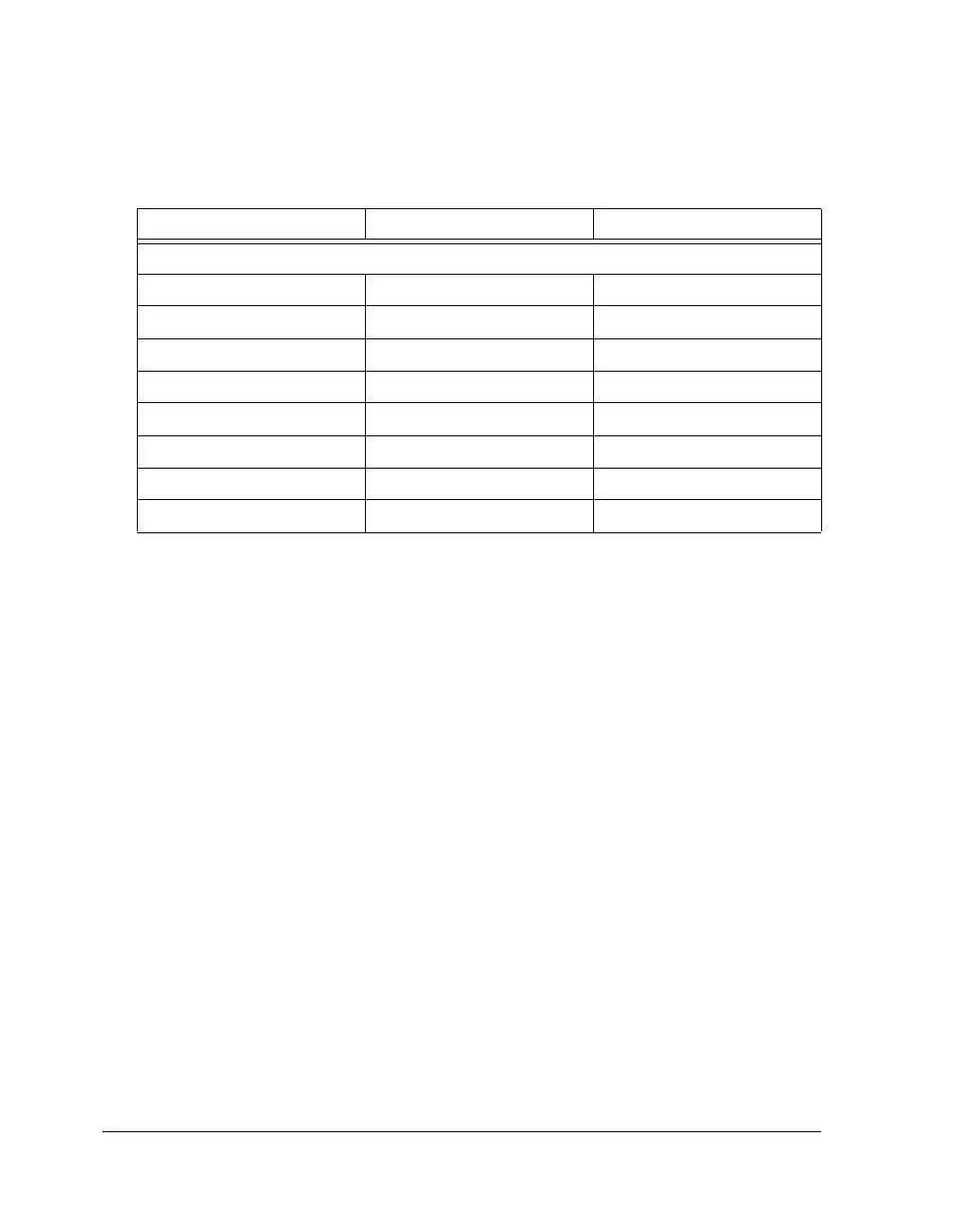

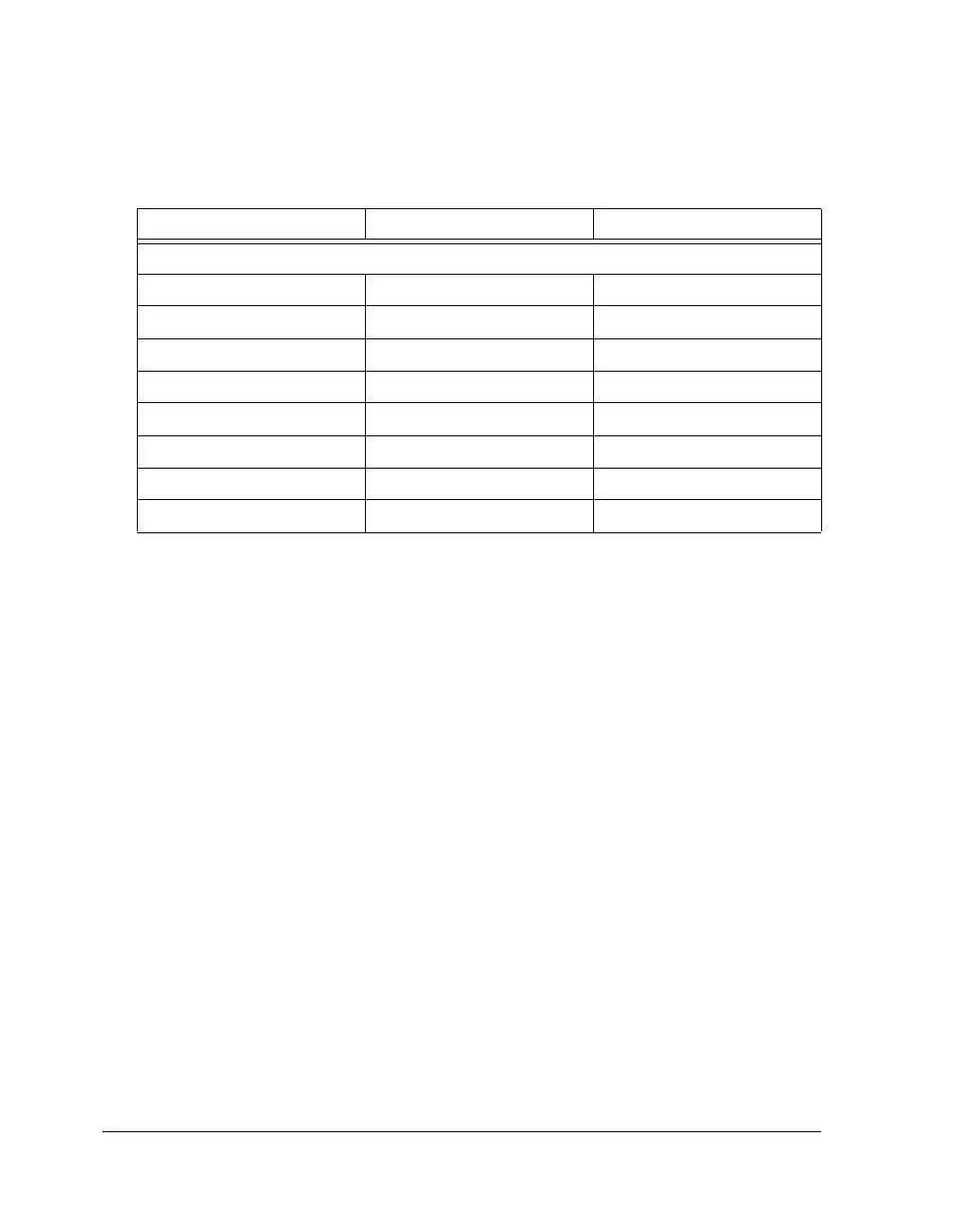

Access Type

Data Buffer No No

Core Data Access N/A N/A

DMA Data Access N/A N/A

DMA Channels N/A N/A

DMA Chaining N/A N/A

Boot Capable N/A N/A

Local Memory No No

Clock Operation f

PCLK

/4 f

PCLK

/4

Table 13-1. S/PDIF Specifications (Cont’d)

Feature Transmitter Receiver

Loading...

Loading...