ADSP-2146x External Port Registers

A-42 ADSP-214xx SHARC Processor Hardware Reference

DLL Status Registers (DLL0STAT0, DLL1STAT0)

The

DLL0STAT0 status register indicates the DLL lock status.

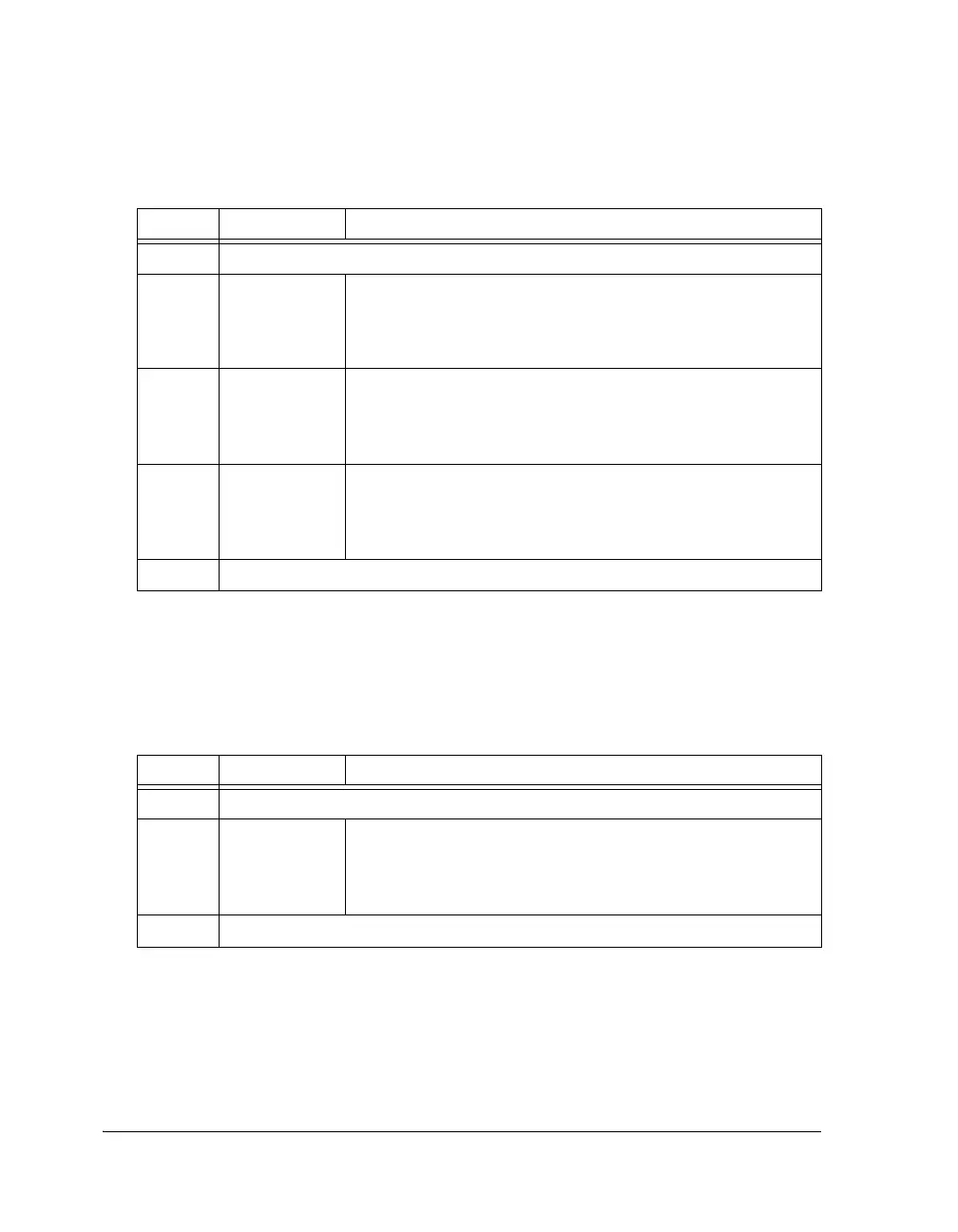

Table A-21. DLL1CTL1 Register Bit Descriptions (RW)

Bit Name Description

8–0 Reserved

9 RESETDLL Reset DLL Control Logic. Active high, when active, it resets the

DLL control logic only, including the 90 degree DQS shifters.

0 = No effect

1 = Reset DLL1 control logic

10 RESETDAT Reset Data Capture Logic. Active high, when active, it resets the

data capture logic only, including P and N buffers.

0 = No effect

1 = Reset DLL1 reset capture logic

11 RESETCAL Reset DQS Phase Calibration Logic. Active high, when active, it

resets the DQS phase calibration logic.

0 = No effect

1 = Reset DLL1 DQS phase calibration logic

31–12 Reserved

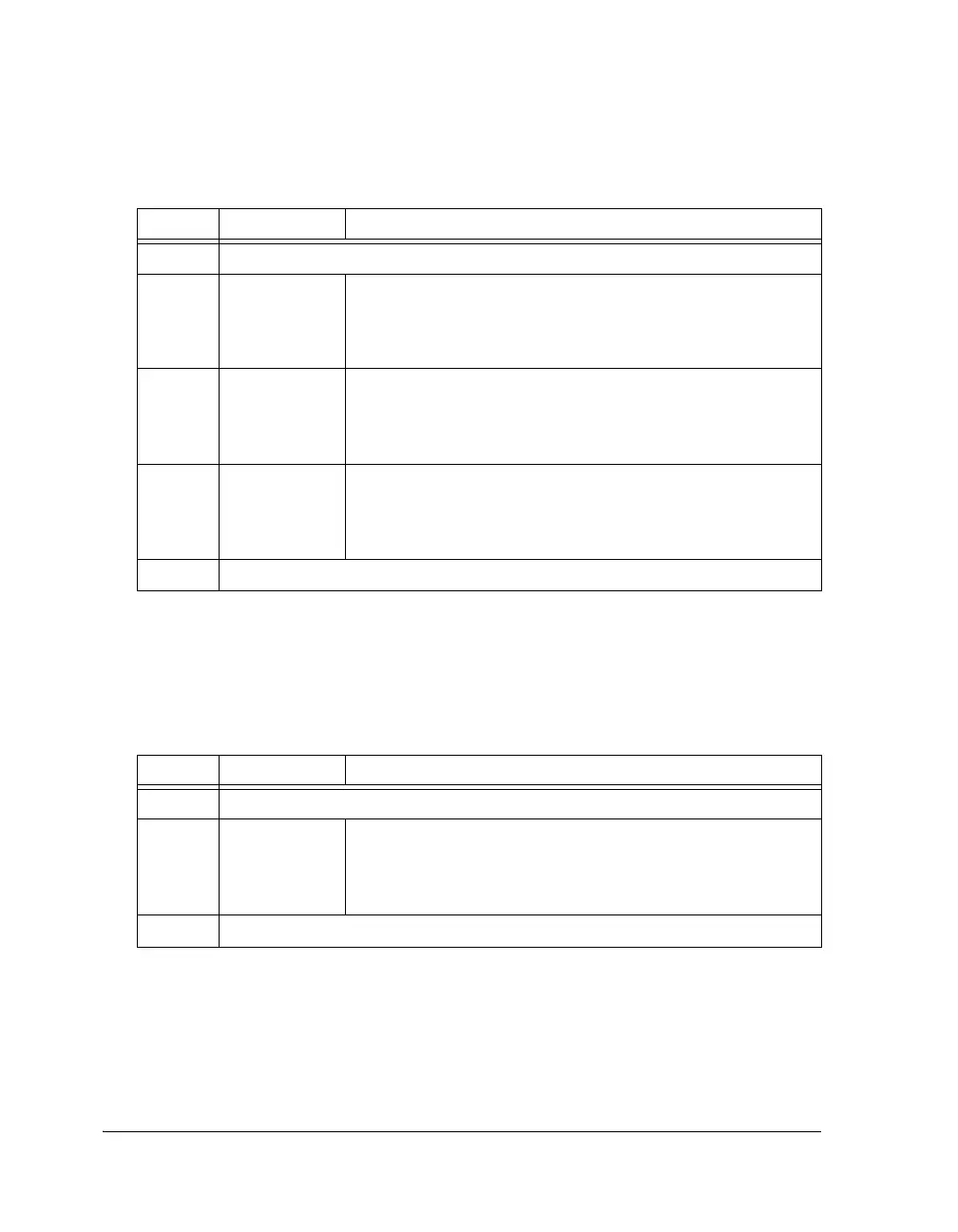

Table A-22. DLL0STAT0 Register Bit Descriptions (RW)

Bit Name Description

0–29 Reserved

30 DLL_LOCKED Reset DLL Control Logic. If this bit is set, indicates that the

on-chip DLL for DDR2 controller has locked. Note after reset

de-asserted the DLL does automatically lock to the default DDR2

CLK frequency even the DDR2C is not enabled.

31 Reserved

Loading...

Loading...