ADSP-214xx SHARC Processor Hardware Reference A-253

Registers Reference

Two Wire Interface Registers

The two wire interface (TWI) registers provide all control and status bits

for this peripheral. Status bits can be updated by their respective func-

tional blocks.

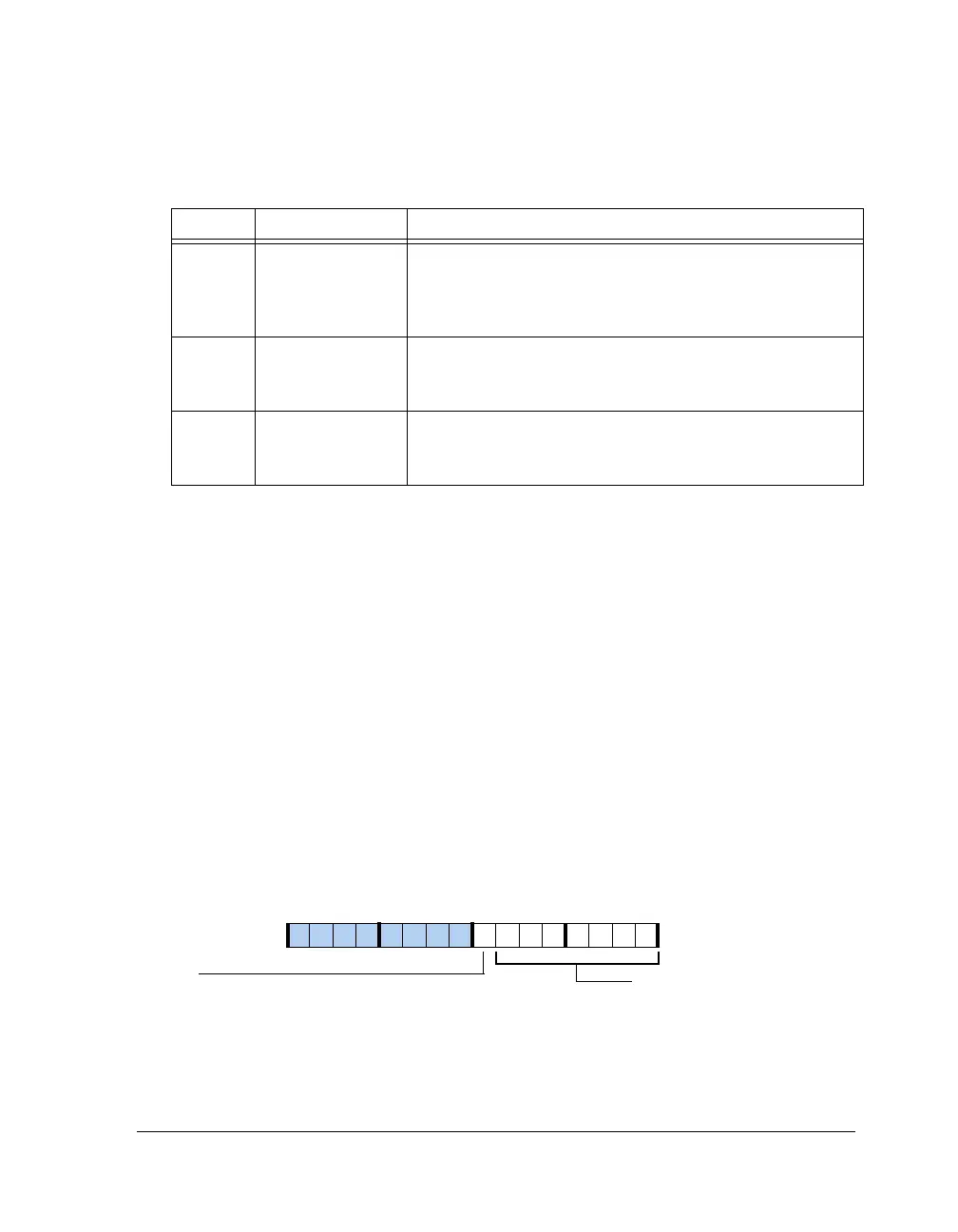

Master Internal Time Register (TWIMITR)

The TWIMITR register, shown in Figure A-143 and described in

Table A-136), is used to enable the TWI module as well as to establish a

relationship between the peripheral clock (PCLK) and the TWI controller’s

internally-timed events. The internal time reference is derived from

PCLK

using the prescaled value:

PRESCALE = f

PCLK

/10 MHz

Table A-135. UART0RXSTAT Register Bit Descriptions (RO)

Bit Name Description

0UARTERRIRQReceive Channel Error Interrupt.

0 = No error interrupt

1 = Error interrupt generated due to receive error (parity/over-

run/framing). This bit is cleared on a read of the LSR register.

1 UARTDMASTAT DMA Status. Provides DMA status.

0 = RX DMA is inactive

1 = RX DMA is active

2 UARTCHSTAT DMA Chaining Status. Provides DMA chaining status.

0 = RX DMA chain loading is inactive

1 = RX DMA chain loading is active

Figure A-143. TWIMITR Register

PRESCALE (6–0)

TWIEN

Prescale

TWI Enable

09 837564 2114 12 11 101315

Loading...

Loading...