ADSP-214xx SHARC Processor Hardware Reference 6-3

FFT/FIR/IIR Hardware Modules

FFT Accelerator

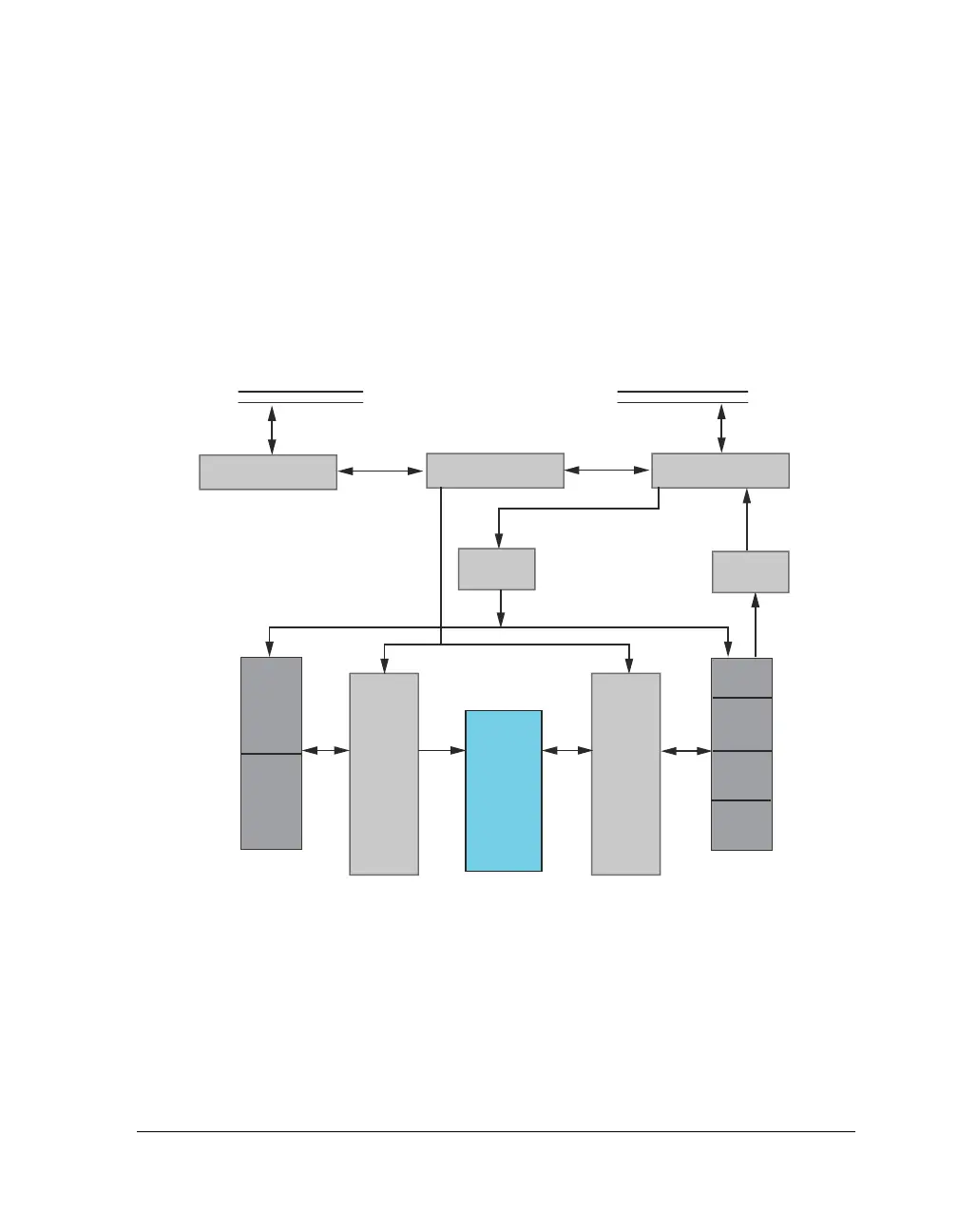

The FFT accelerator (shown in Figure 6-1) implements radix-2 complex

floating-point FFT. The accelerator’s data and twiddle coefficient inter-

face is designed to connect to the processor’s DMA engine (acting like a

peripheral) and implements a synchronous pipeline read/write protocol

with a pipeline depth of 1.

Figure 6-1. FFT Block Diagram

CORE PMD/DMD

BUS

IOD0

BUS

FFT

COMPUTE

UNIT

(Complex

Butterfly)

COEFF

ACCESS

CONTROL

DATA

ACCESS

CONTROL

C

O

E

F

F

I

C

I

E

N

T

S

FFT CONTROL

REGISTERS

DMA

CONTROLLER

FFT CONTROLLER

OUTPUT

BUFFER

INPUT

BUFFER

D

A

T

A

256x4

256x2

Loading...

Loading...