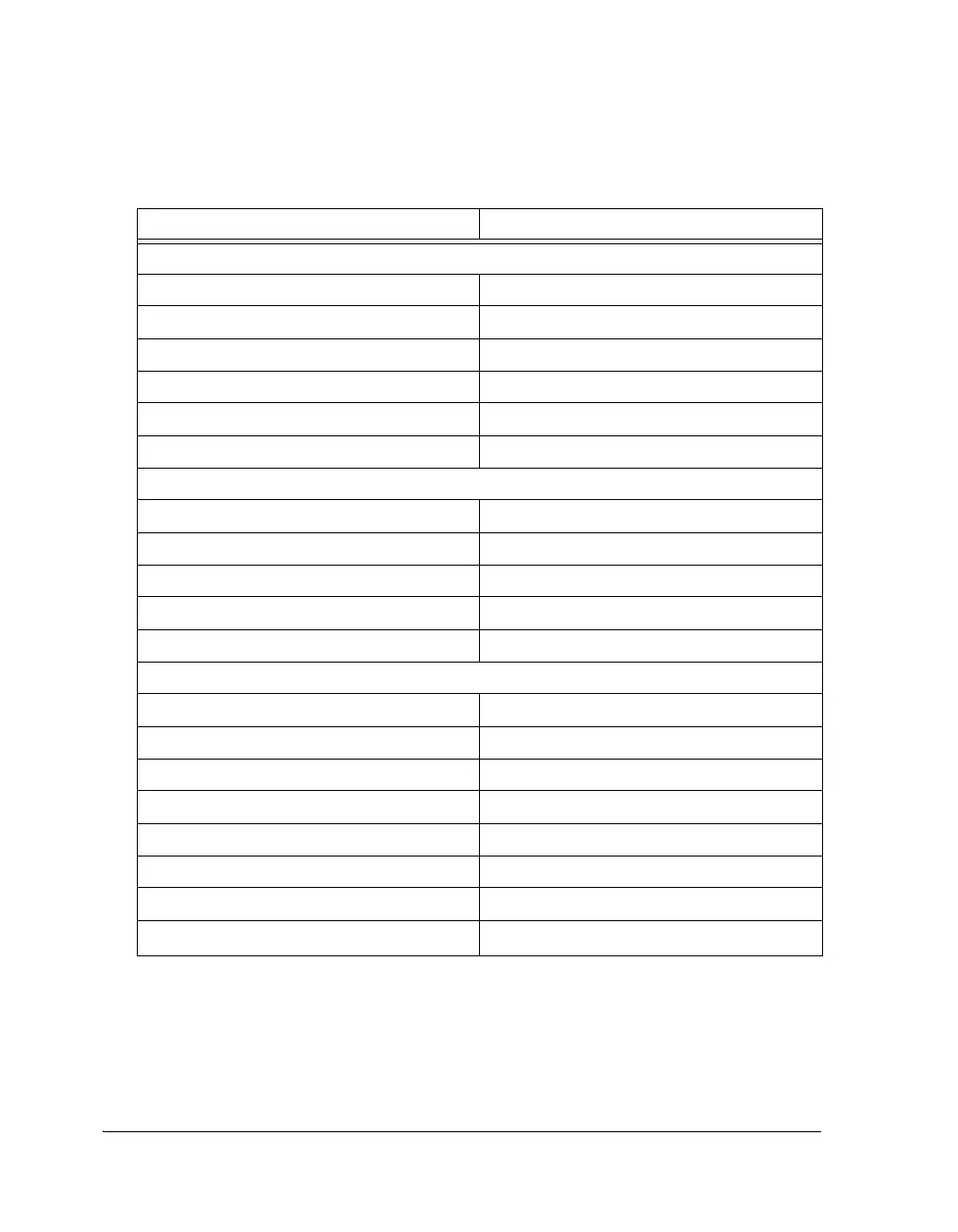

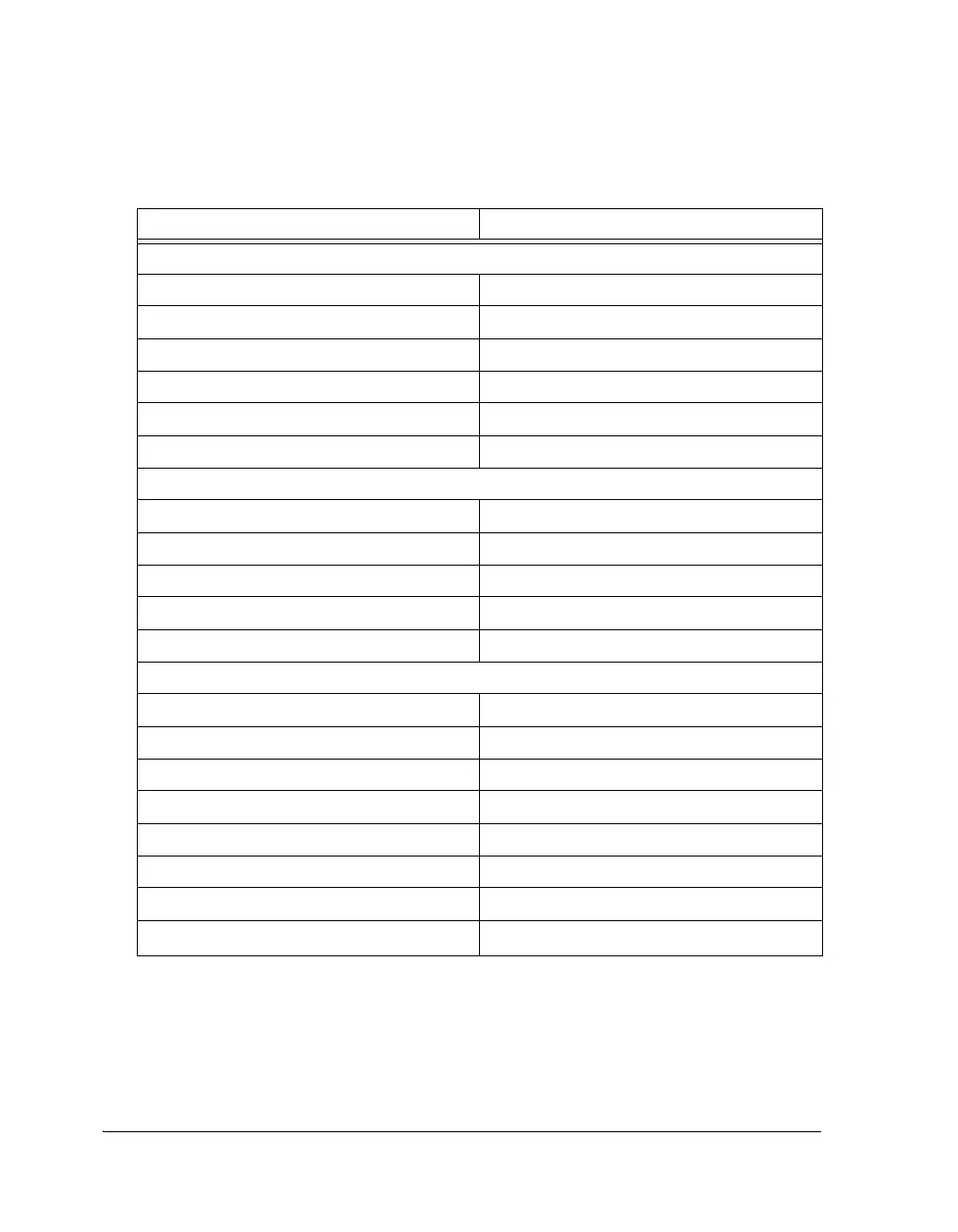

6-2 ADSP-214xx SHARC Processor Hardware Reference

Table 6-1. Accelerator Specifications

Feature FFT/FIR/IIR

Connectivity

Multiplexed Pinout No

SRU DAI Required No

SRU DAI Default Routing N/A

SRU2 DPI Required No

SRU2 DPI Default Routing N/A

Interrupt Control Yes

Protocol

Master Capable N/A

Slave Capable N/A

Transmission Simplex N/A

Transmission Half Duplex N/A

Transmission Full Duplex N/A

Access Type

Data Buffer Yes

Core Data Access No

DMA Data Access Yes

DMA Channels 2

DMA Chaining Yes

Boot Capable N/A

Local Memory Yes (RAM)

Clock Operation f

PCLK

Loading...

Loading...