ADSP-214xx SHARC Processor Hardware Reference 11-11

Input Data Port

This mode sends one 32-bit word to FIFO for each input clock cycle—the

DMA transfer rate matches the PDAP input clock rate.

Packing by 2

Packing by 2 moves data in two cycles. Each input word can be up to 16

bits wide.

• On clock edge 1, bits 19–4 are moved to bits 15–0 (16 bits)

• On clock edge 2, bits 19–4 are moved to bits 31–16 (16 bits)

This mode sends one packed 32-bit word to FIFO for every two input

clock cycles—the DMA transfer rate is one-half the PDAP input clock

rate.

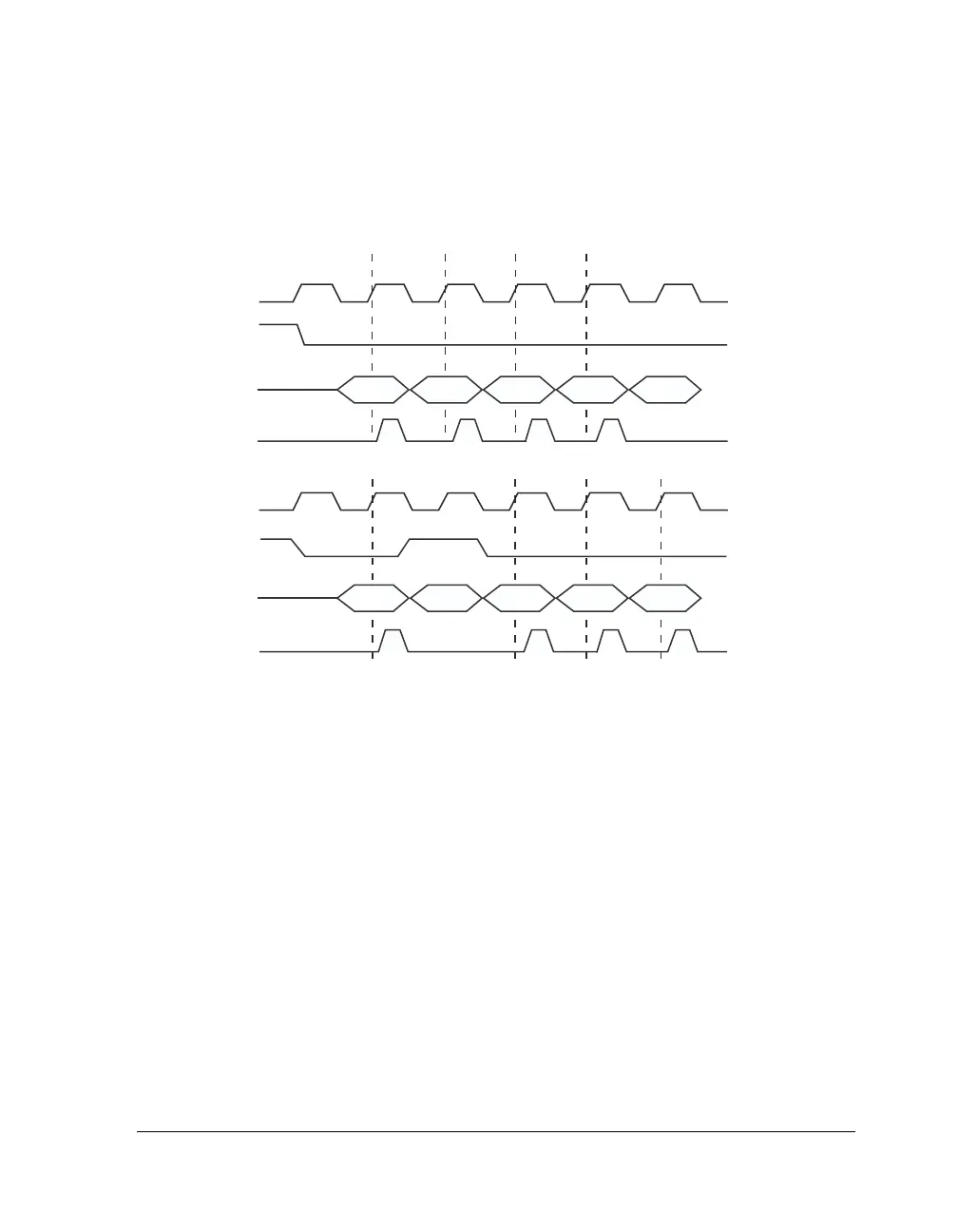

Figure 11-3. PDAP Hold Input (No Packing)

PDAP_CLK_I

PDAP DATA

PDAP_HOLD_I

W0 W1 W2

W3

W4

W0 W1 W2

W3

PDAP_STROBE_O

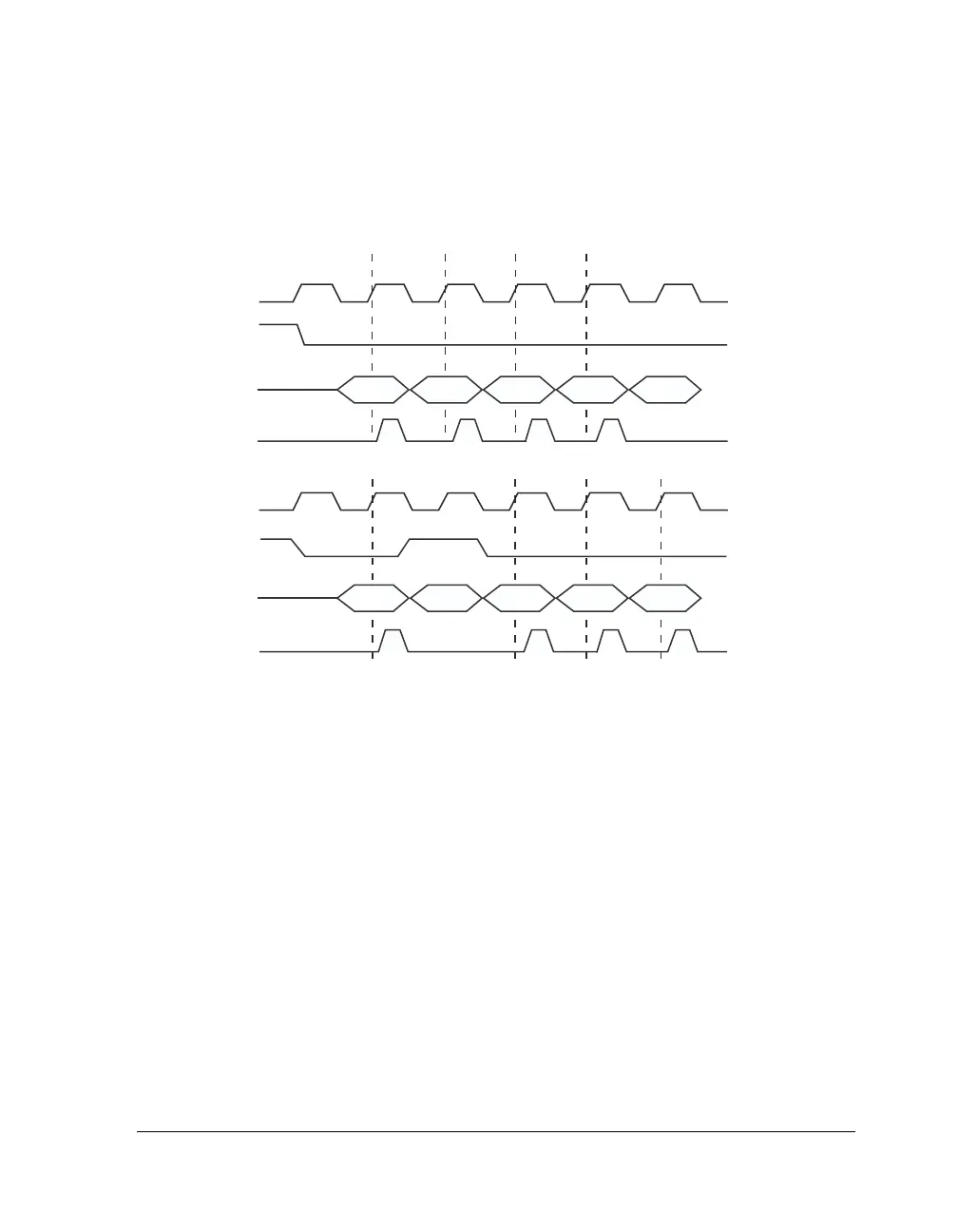

PDAP_CLK_I

PDAP DATA

PDAP_HOLD_I

PDAP_STROBE_O

Loading...

Loading...