ADSP-214xx SHARC Processor Hardware Reference 11-23

Input Data Port

These are sticky bits that must be cleared by writing to the

IDP_CLROVR bit

(bit 6 of the IDP_CTL0 register). When an overflow occurs, incoming data

from IDP channels is not accepted into the FIFO, and data values are lost.

New data is only accepted once space is again created in the FIFO.

Interrupts

This section describes the different types of interrupts used by the inter-

face. Table 11-9 provides an overview of IDP interrupts.

Interrupt Acknowledge

The correct handling of the IDP interrupt requires that the ISR must read

the DAI_IMASK_x register to clear the interrupt latch appropriately. Note

that many interrupts are combined in the DAI interrupt. Refer to “Inter-

rupts” on page 9-32.

Threshold Interrupts

When using the interrupt scheme, the IDP_NSET bits (bits 3-0 of the

IDP_CTL0 register) can be set to N, so N + 1 data can be read from the

FIFO in the interrupt service routine (ISR). The

IDP_FIFO_GTN_INT bit in

DAI_IMASK_X register allows to fire flexible interrupts in order to respond

with the core under different system conditions.

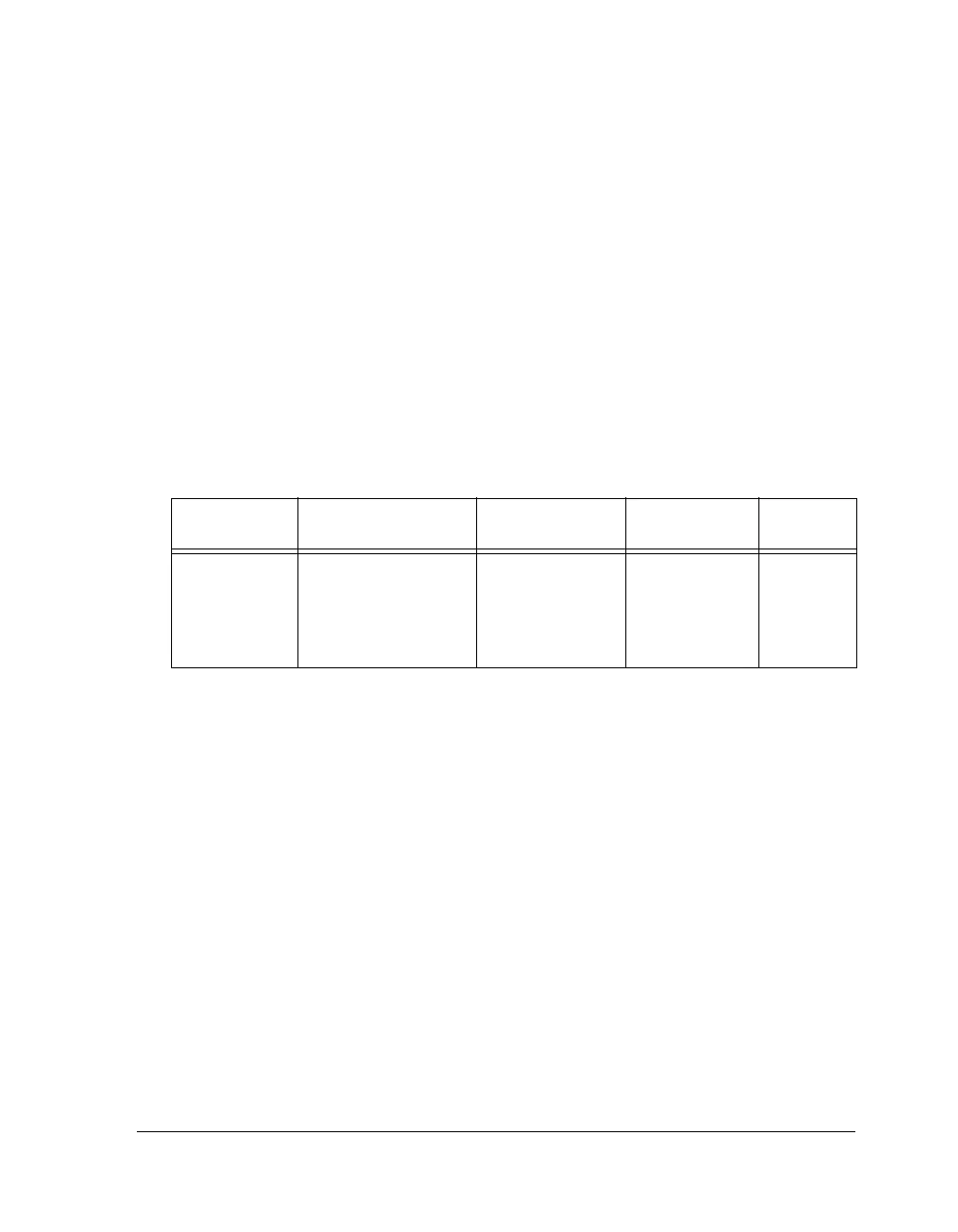

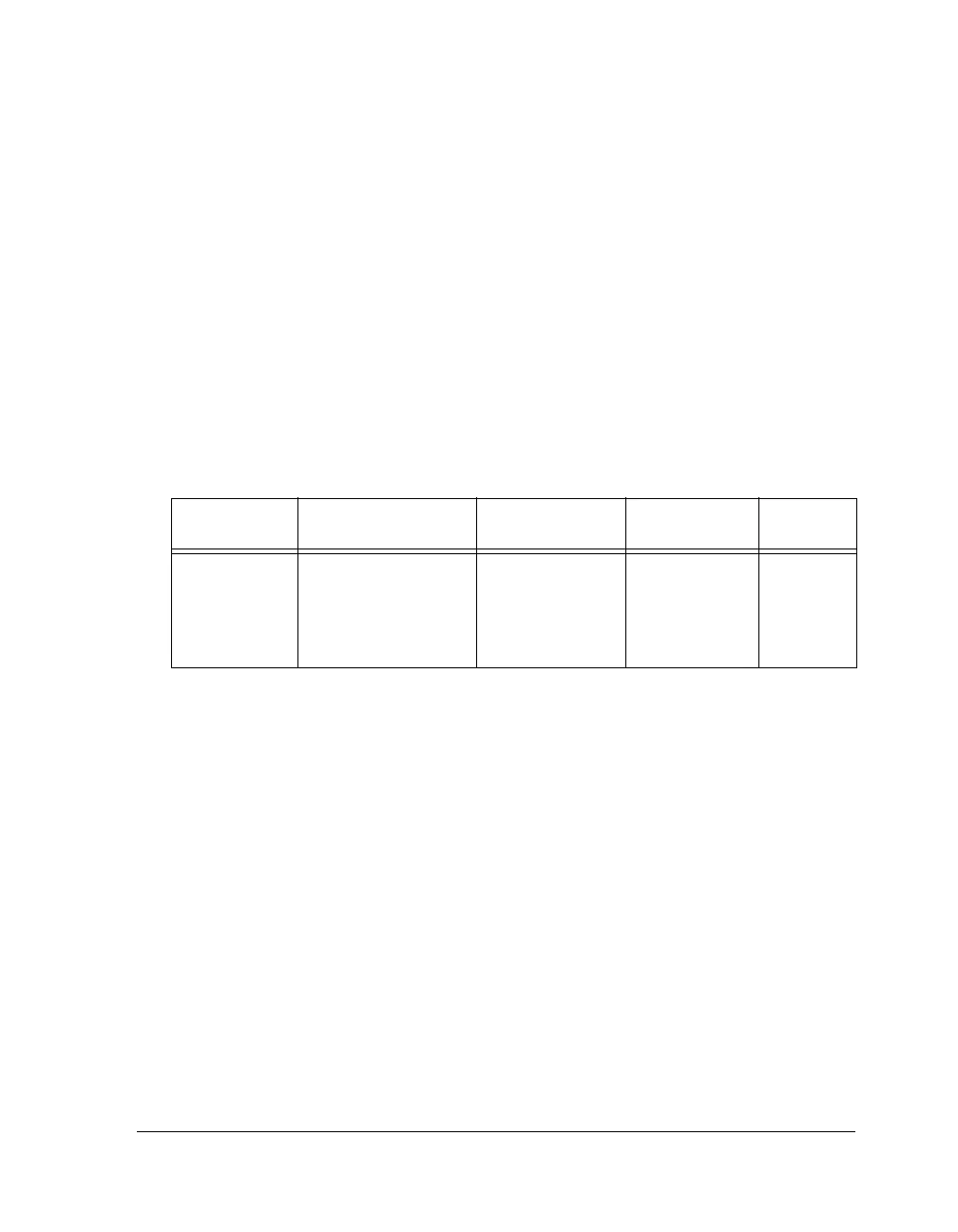

Table 11-9. IDP Interrupt Overview

Interrupt

Sources

Interrupt Condition Interrupt

Completion

Interrupt

Acknowledge

Default IVT

DAI IDP

(I2S, left/right

justified, TDM,

8 channels)

– DMA RX done

– Core RX buffer size

exceeded

– RX buffer overflow

error

Internal transfer

completion

Read-to-clear

DAI_IMASK_x

+ RTI instruc-

tion

P0I, P12I

Loading...

Loading...