DAI Signal Routing Unit Registers

A-148 ADSP-214xx SHARC Processor Hardware Reference

DAI Pin Buffer Registers

The DAI_STAT register, shown in Figure A-97 and described in

Table A-94, and the

DAI_PIN_STAT register, shown in Figure A-83 on

page A-149, provide status information for the IDP/PDAP DMA

channels.

Pin Buffer Registers (DAI_PIN_STAT)

The

DAI_PIN_STAT register, shown in Figure A-83, provides DAI pin buf-

fer status information. This register is updated at up to the

PCLK/2 rate.

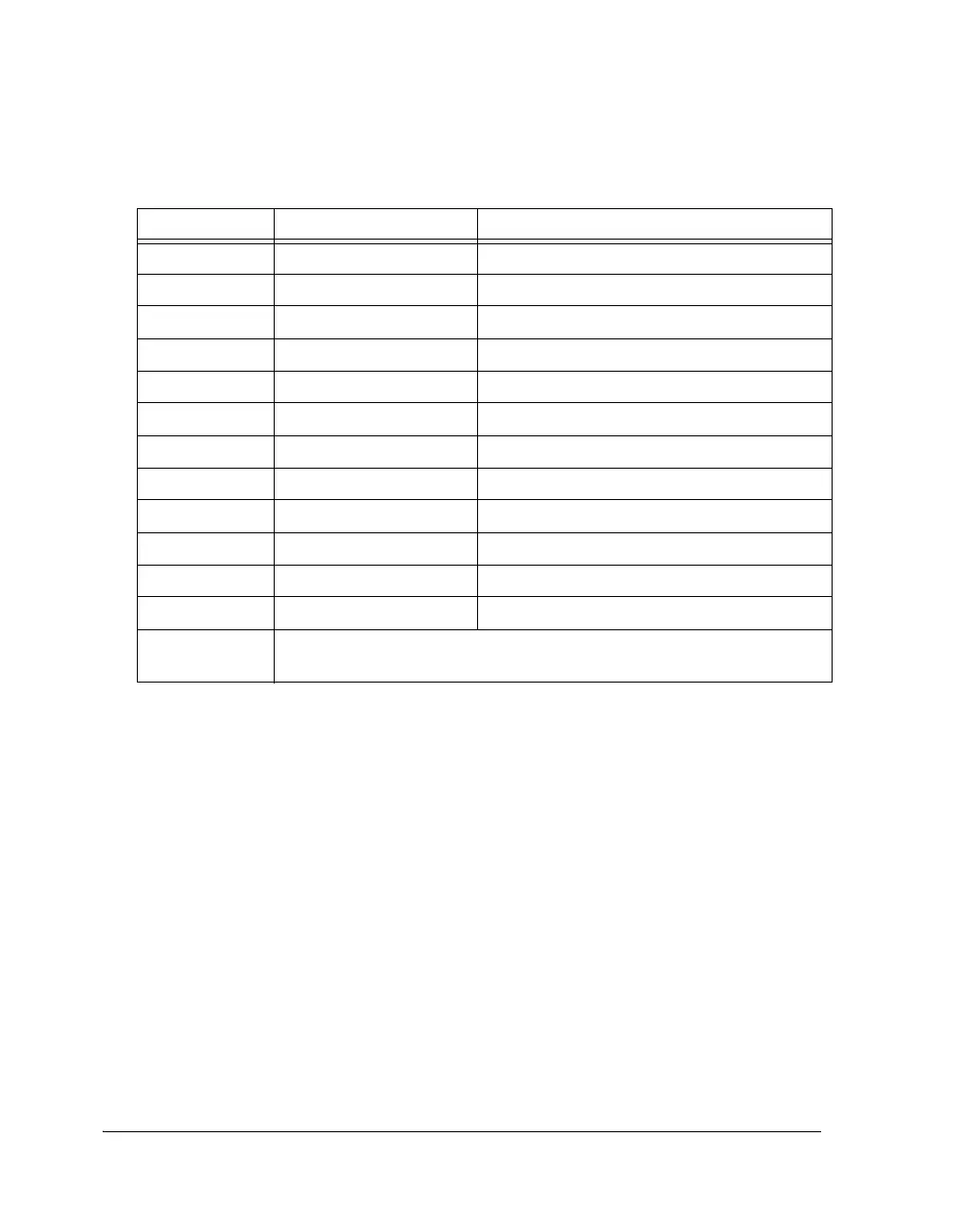

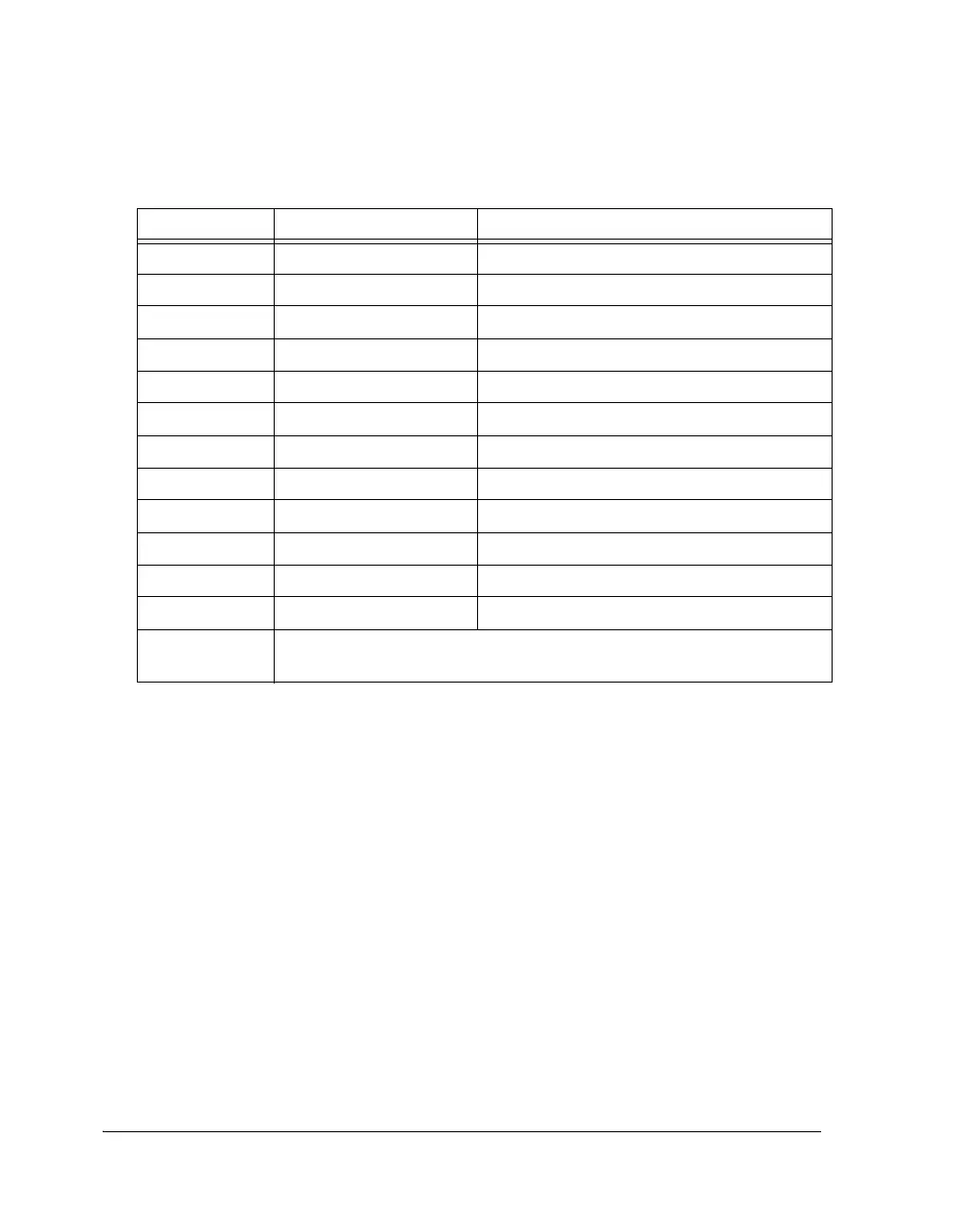

01111 (0xF) SPORT6_DB_O Sport 6 Data Channel B

10000 (0x10) SPORT7_DA_O Sport 7 Data Channel A

10001 (0x11) SPORT7_DB_O Sport 7 Data Channel B

10010 (0x12) SR_SDI External SR_SDI Pin

10011 (0x13) DAI_P01_O DAI External Pin 1

10100 (0x14) DAI_P02_O DAI External Pin 2

10101 (0x15) DAI_P03_O DAI External Pin 3

10110 (0x16) DAI_P04_O DAI External Pin 4

10111 (0x17) DAI_P05_O DAI External Pin 5

11000 (0x18) DAI_P06_O DAI External Pin 6

11001 (0x19) DAI_P07_O DAI External Pin 7

11010 (0x1A) DAI_P08_O DAI External Pin 8

11011 (0x1B) –

11111 (0x1F)

Reserved

Table A-82. Group G Sources – Shift Register Data Routing (Cont’d)

Selection Code Source Signal Description (Output Source Selection)

Loading...

Loading...