ADSP-214xx SHARC Processor Hardware Reference 6-59

FFT/FIR/IIR Hardware Modules

• A DMA bus interface for transferring data to and from the acceler-

ator. This interface is also used to preload the coefficients and Dks

at start up.

• DMA configuration registers for the transfer of input data, output

data and coefficients

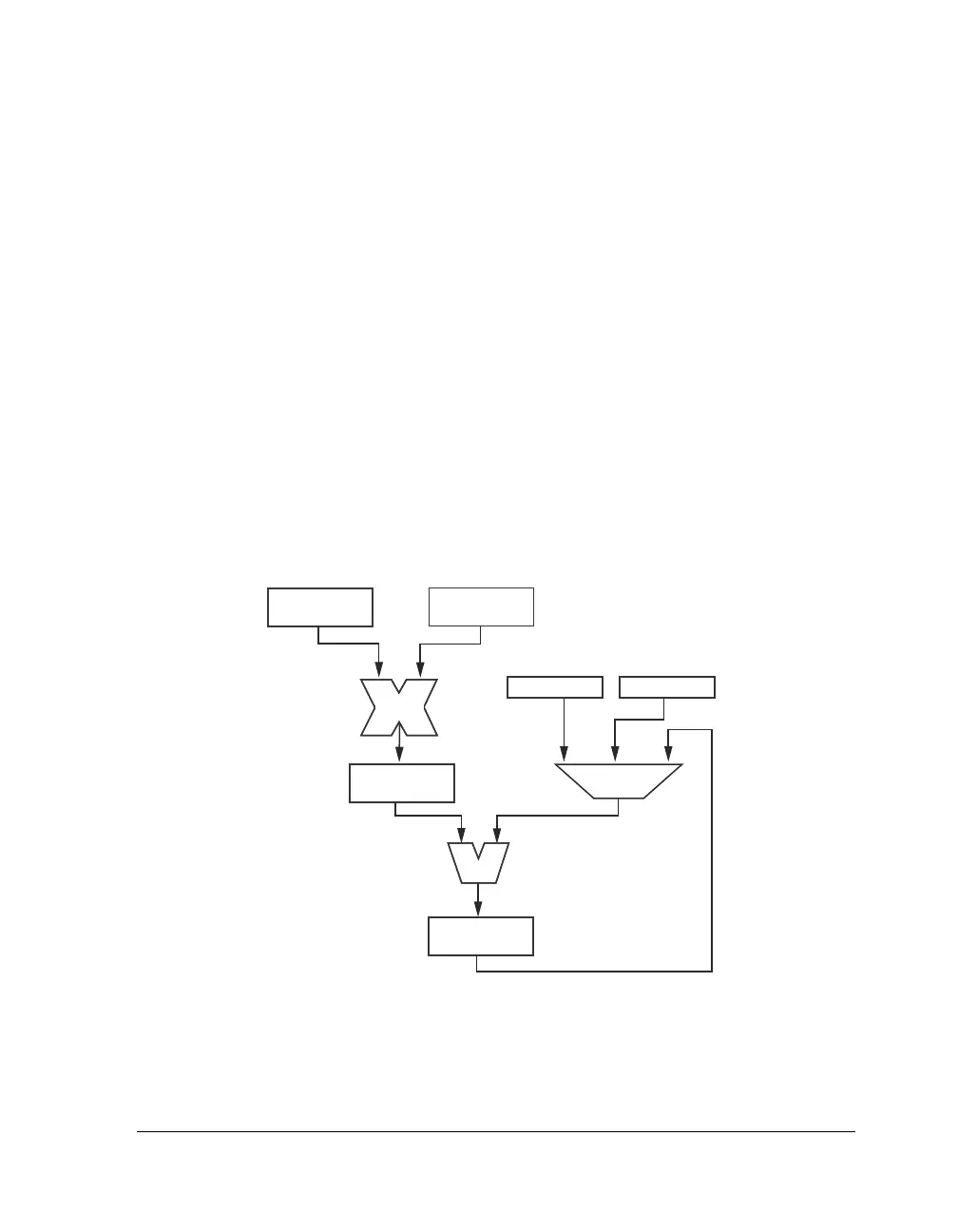

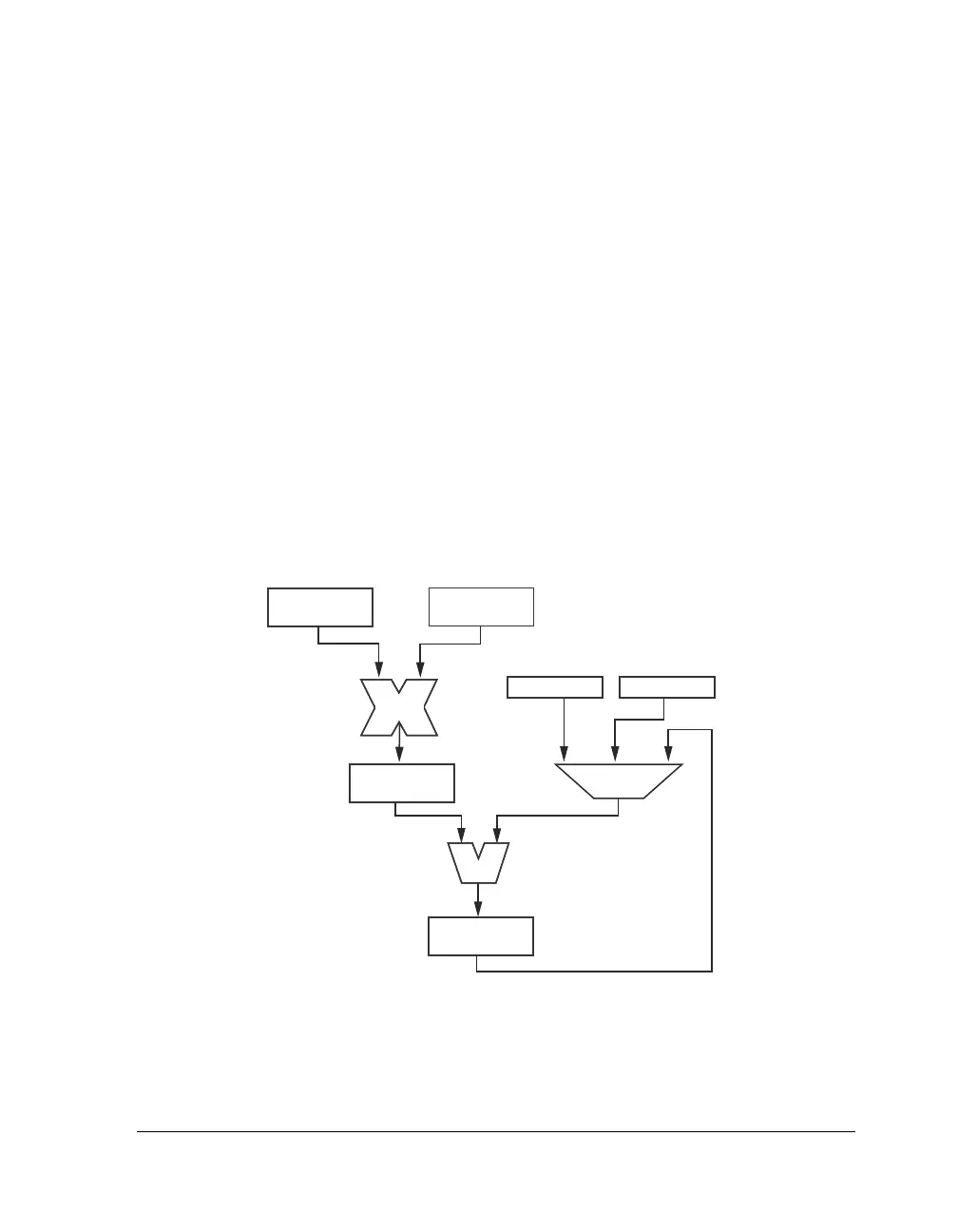

Multiply and Accumulate (MAC) Unit

The MAC unit shown in Figure 6-11 has a pipelined multiplier and accu-

mulator unit that operates on the data and coefficient fetched from the

data and coefficient memory. The MAC can perform either 32-bit float-

ing-point or 40-bit floating-point MAC operations. 32-bit floating-point

operations generate 32-bit results and 40-bit floating-point operations

generate 40-bit results.

Figure 6-11. IIR MAC Unit

MULT

ADDER

DATA REGISTER

dk1 REGISTER

COEFFICIENT

REGISTER

dk2 REGISTER

MULT RESULT

REGISTER

MAC RESULT

REGISTER

MUX

Loading...

Loading...