ADSP-214xx SHARC Processor Hardware Reference 14-15

Precision Clock Generator

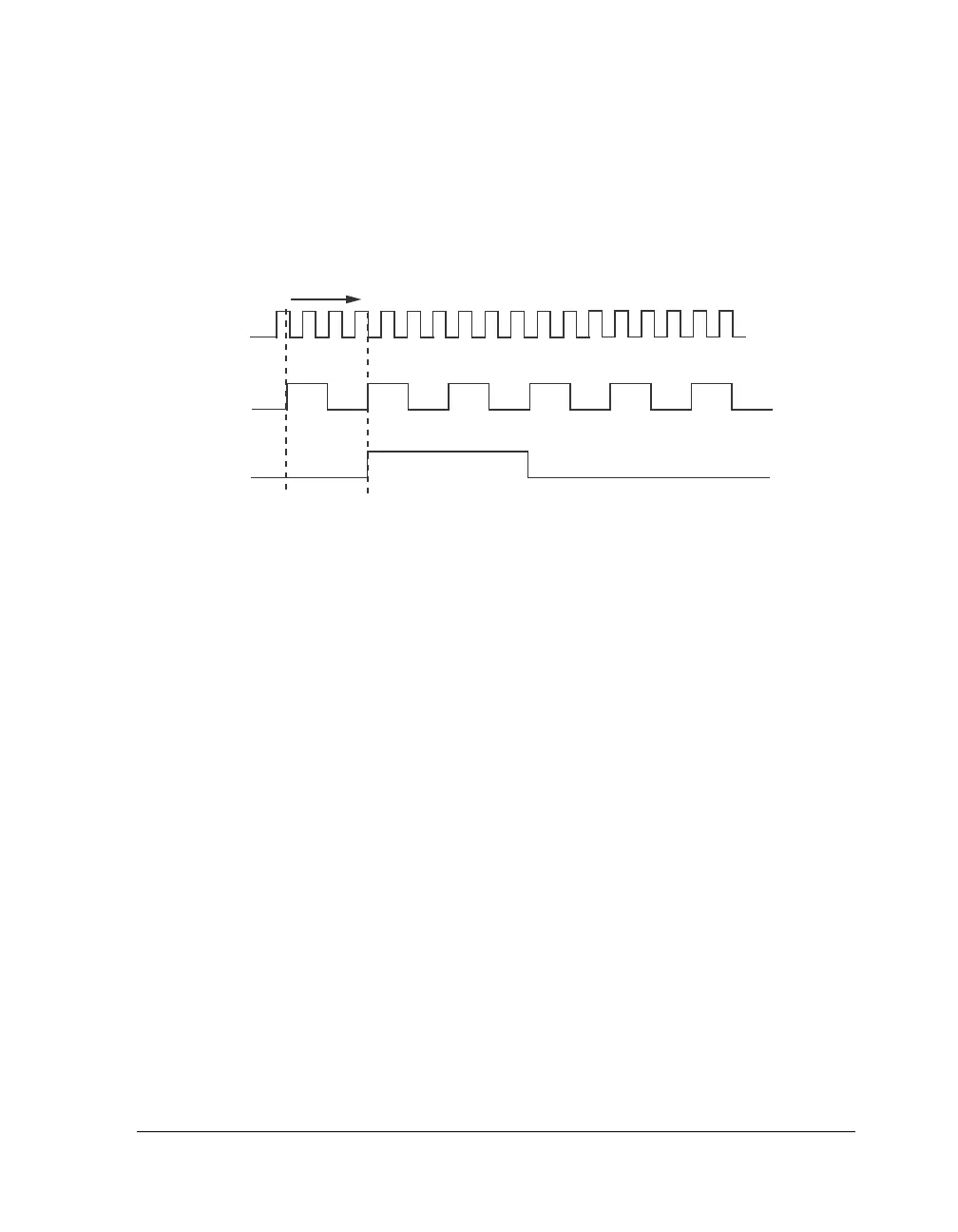

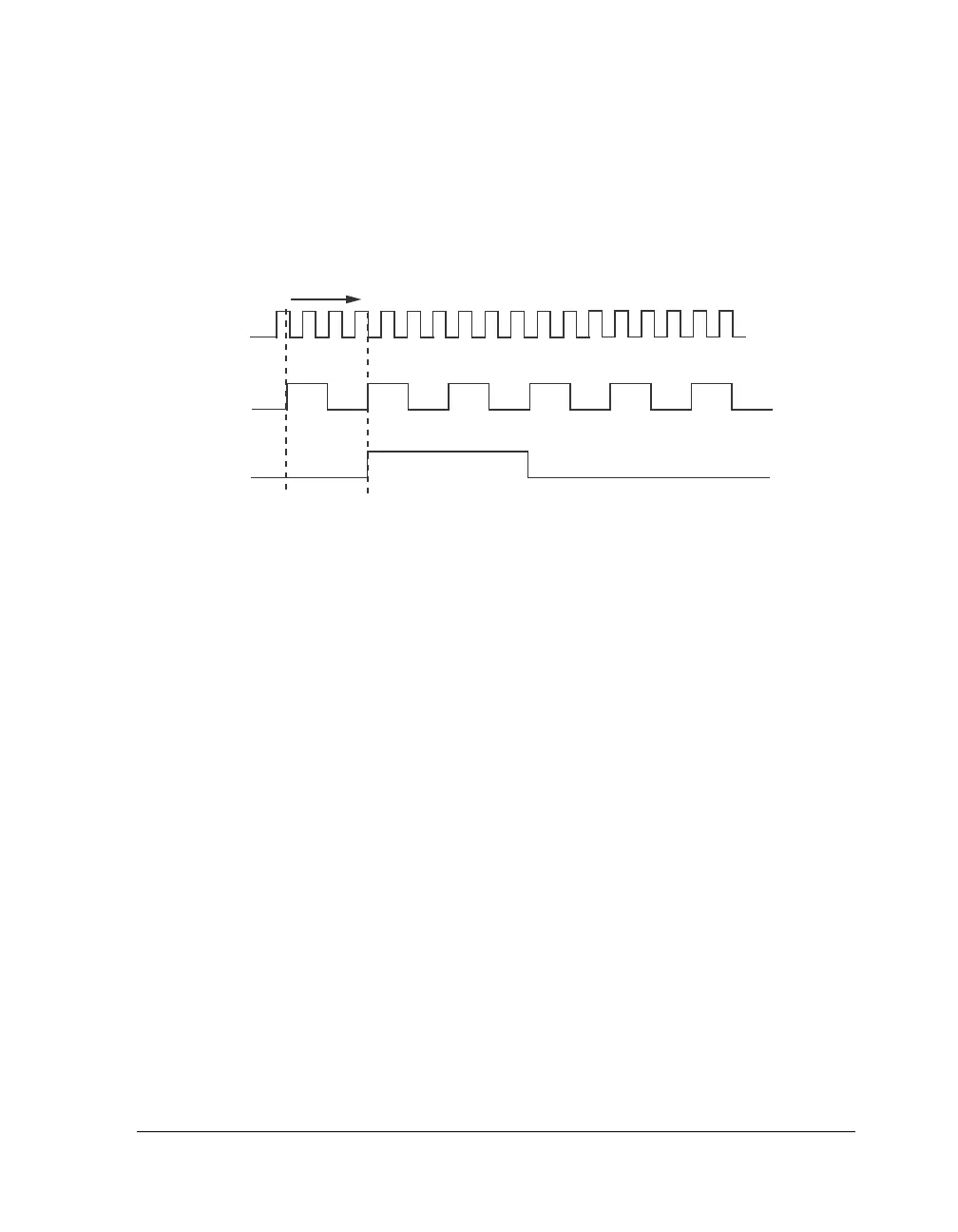

Since the rising edge of the external clock is used to synchronize with the

frame sync, the frame sync output is not generated until a rising edge of

the external clock is sensed (Figure 14-5).

External Event Trigger Delay

The time delay between the rising trigger edge and the start of

SCLK/FS

varies between 2.5 to 3.5 input clock periods. If the input clock and the

trigger signal are synchronous, the delay is 3 input clock periods. The fol-

lowing cases need to be considered:

• PCLK is the input source. In this case if the given trigger event is

synchronous to PCLK, the delay is 3 PCLK periods. If the trigger sig-

nal is asynchronous with PCLK, the delay varies from 2.5 PCLK

periods to 3.5

PCLK periods. (It depends on whether the trigger

edge occurs in the positive half cycle or negative half cycle of PCLK.)

•

CLKIN is the input source. In this case if the given trigger signal is

synchronous to

CLKIN, the delay is 3 CLKIN periods. But if they are

asynchronous to CLKIN, the delay can vary between 2.5 CLKIN peri-

ods to 3.5

CLKIN periods.

Figure 14-5. FS Output Synchronization With External Trigger Input

CLKIN

(INPUT)

EXT. TRIGGER

(INPUT)

FSA

(OUTPUT)

TRIGGER DELAY

Loading...

Loading...