FIR Accelerator

6-44 ADSP-214xx SHARC Processor Hardware Reference

The FIRCTL2 register is part of the FIR TCB. This allows program-

ming individual FIR channels with different control attributes.

Interrupts

The FIR accelerator has two interrupts (Table 6-3) that are programmable

through the programmable interrupt priority control register

(see Appendix B, Peripheral Interrupt Control). Source bits ACC0I and

ACC1I are used to connect FIR interrupts to the peripheral interrupt inputs

of the core.

One interrupt line is shared by all the DMA interrupts and the other by

MAC status interrupts. Separate status registers are provided to further

differentiate the various sources.

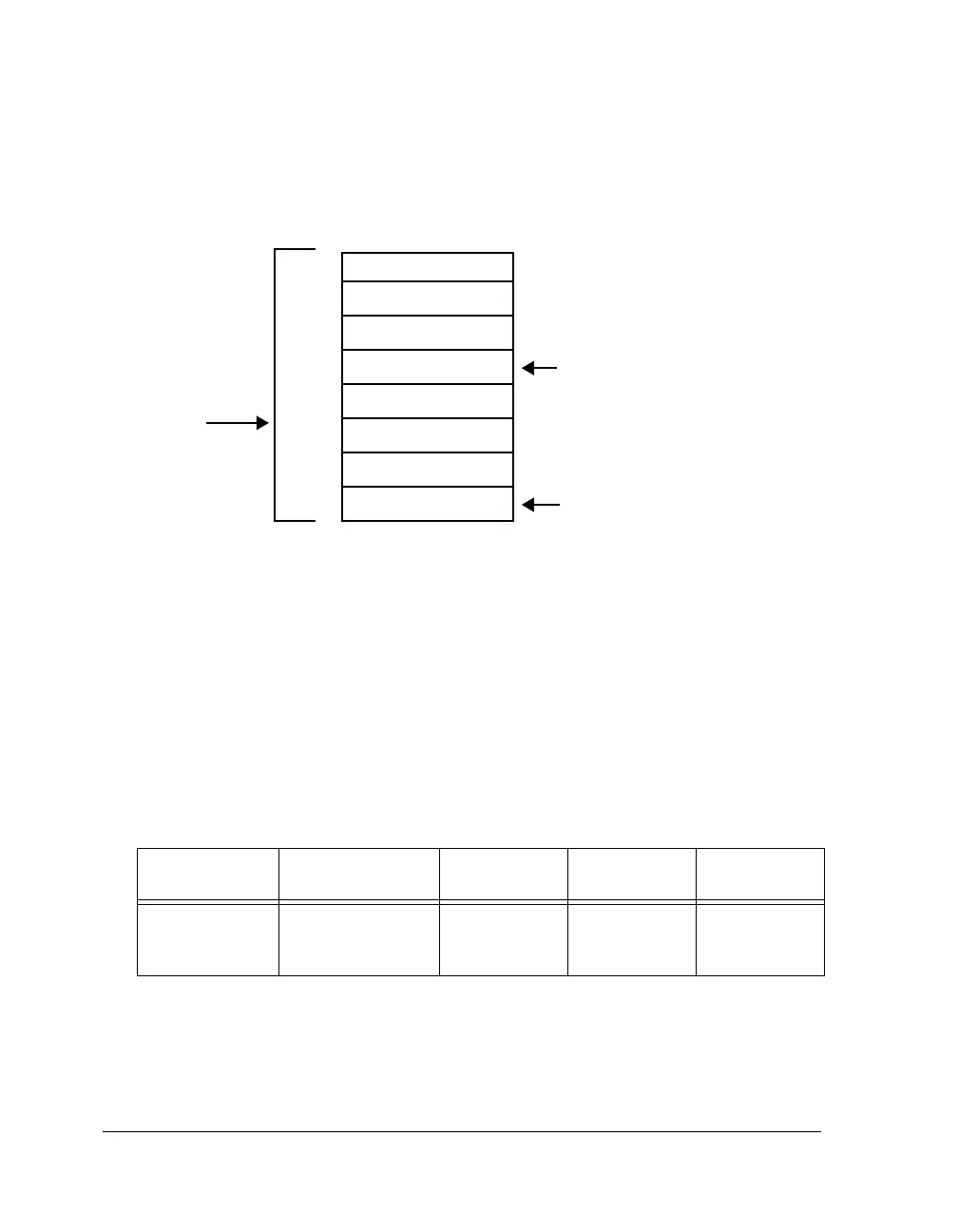

Figure 6-7. Circular Buffer Addressing

Table 6-3. Overview of FIR Interrupts

Interrupt Source Interrupt Condition Interrupt

Completion

Interrupt

Acknowledge

Default IVT

FIR (2 channels) - Window Complete

- Channel Complete

- MAC status

- internal trans-

fer completion

RTI instruction Need to route

ACCx1 (PICRx)

to any PxxI

20

19

5

4

2

3

1

.

.

.

Index Register

Base Register

Buffer Length

Register

Loading...

Loading...