ADSP-214xx SHARC Processor Hardware Reference A-15

Registers Reference

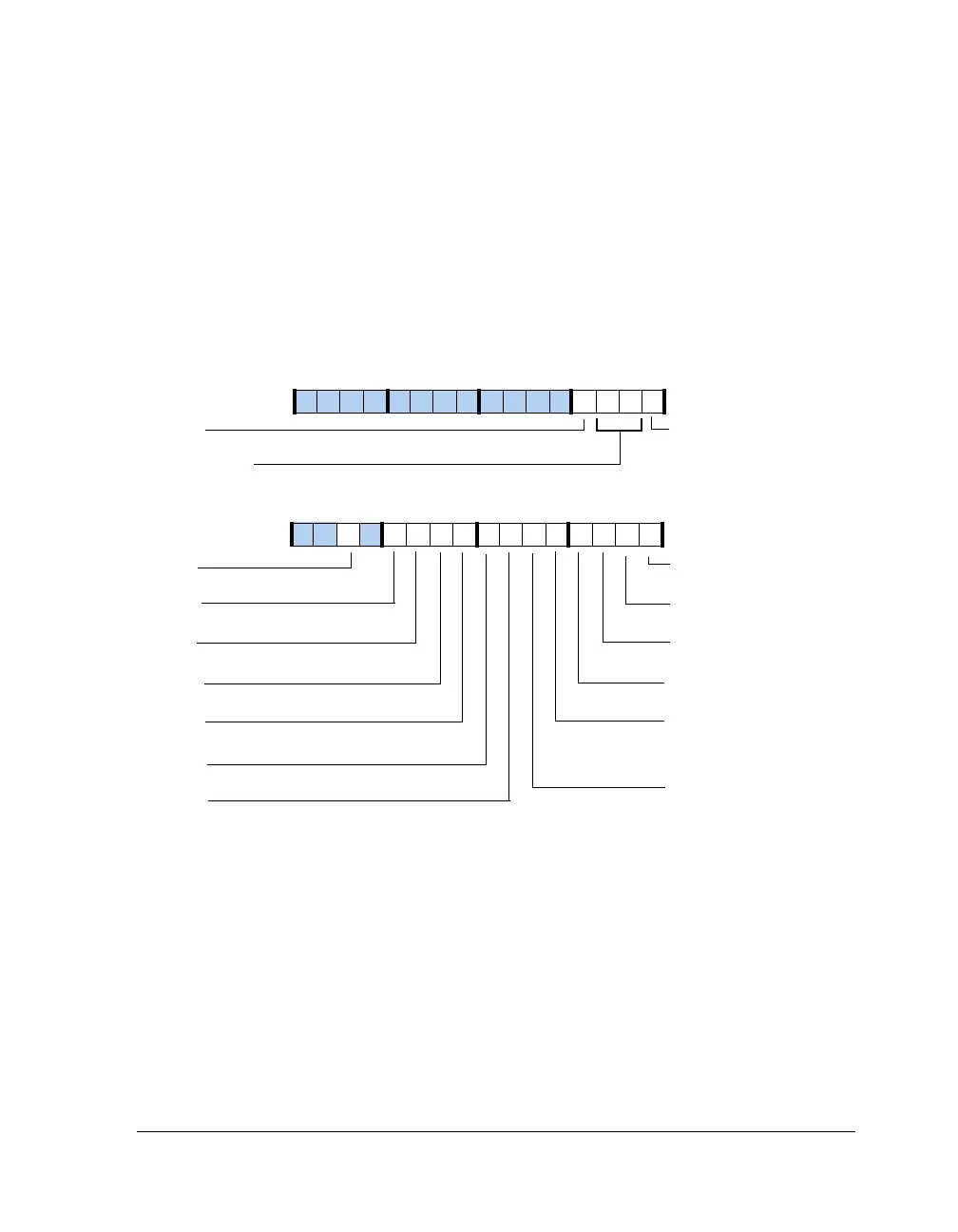

Power Management Control Register 1

(PMCTL1)

This register contains the bits for shutting down the clocks to various

peripherals and selecting one of the three FIR/IIR/FFT accelerators. The

core can write to bits 19–0 of this register.

Writes to this register have an effect latency of two PCLK cycles.

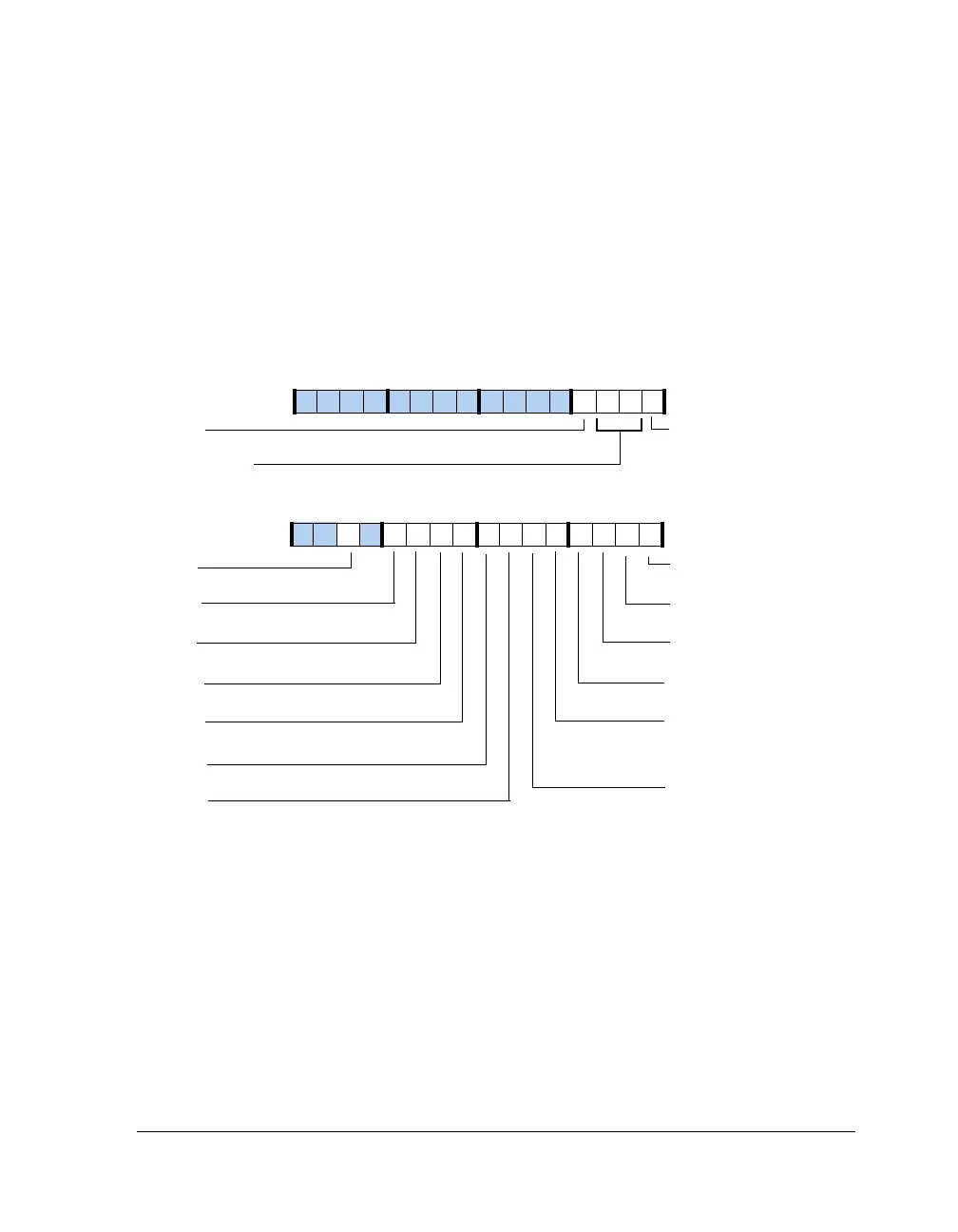

Figure A-5. PMCTL1 Register

RTCOFF

ACCOFF

Accelerator Clocks

Shutdown

ACCSEL (18–17)

Accelerator Select

UART0POFF

UART Clock Shutdown

MLBOFF

MLB Clock Shutdown

RTC Clock Shutdown

TWIOFF

TWI Clock Shutdown

PWMOFF

PWM Clock Shutdown

DTCPOFF

DTCP Clock Shutdown

DAIOFF

Shutdown Clock to SRC,

SPDIF, SRU, PCG, DAI, IDP,

PDAP

EPOFF

EP Clock Shutdown

SP01OFF

SP0/1 Clock Shutdown

SP23OFF

SP2/3 Clock Shutdown

SP67OFF

SP6/7 Clock Shutdown

SP45OFF

SP4/5 Clock Shutdown

TMROFF

Timer Clock Shutdown

SPIOFF

SPI Clock Shutdown

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...