Operating Modes

16-10 ADSP-214xx SHARC Processor Hardware Reference

PWM Waveform Generation

If the

PRDCNT bit is set, the internally-clocked timer generates rectangular

signals with well-defined period and duty cycles. This mode also generates

periodic interrupts for real-time processing.

The 32-bit period (

TMxPRD) and width (TMxW) registers are programmed

with the values of the timer count period and pulse width modulated out-

put pulse width.

When the timer is enabled in this mode, the TIMERx signal is pulled to a

deasserted state each time the pulse width expires, and the signal is

asserted again when the period expires (or when the timer is started).

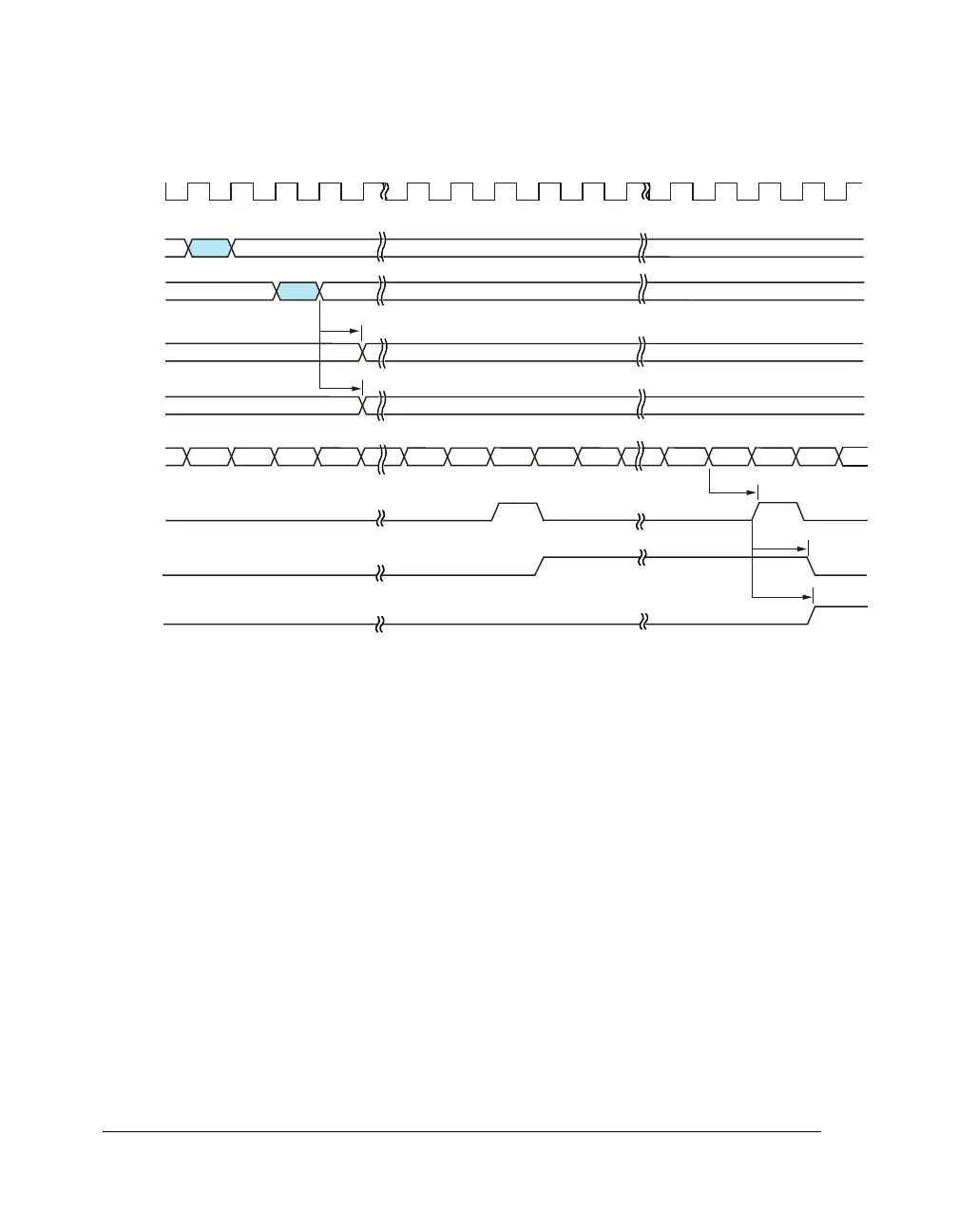

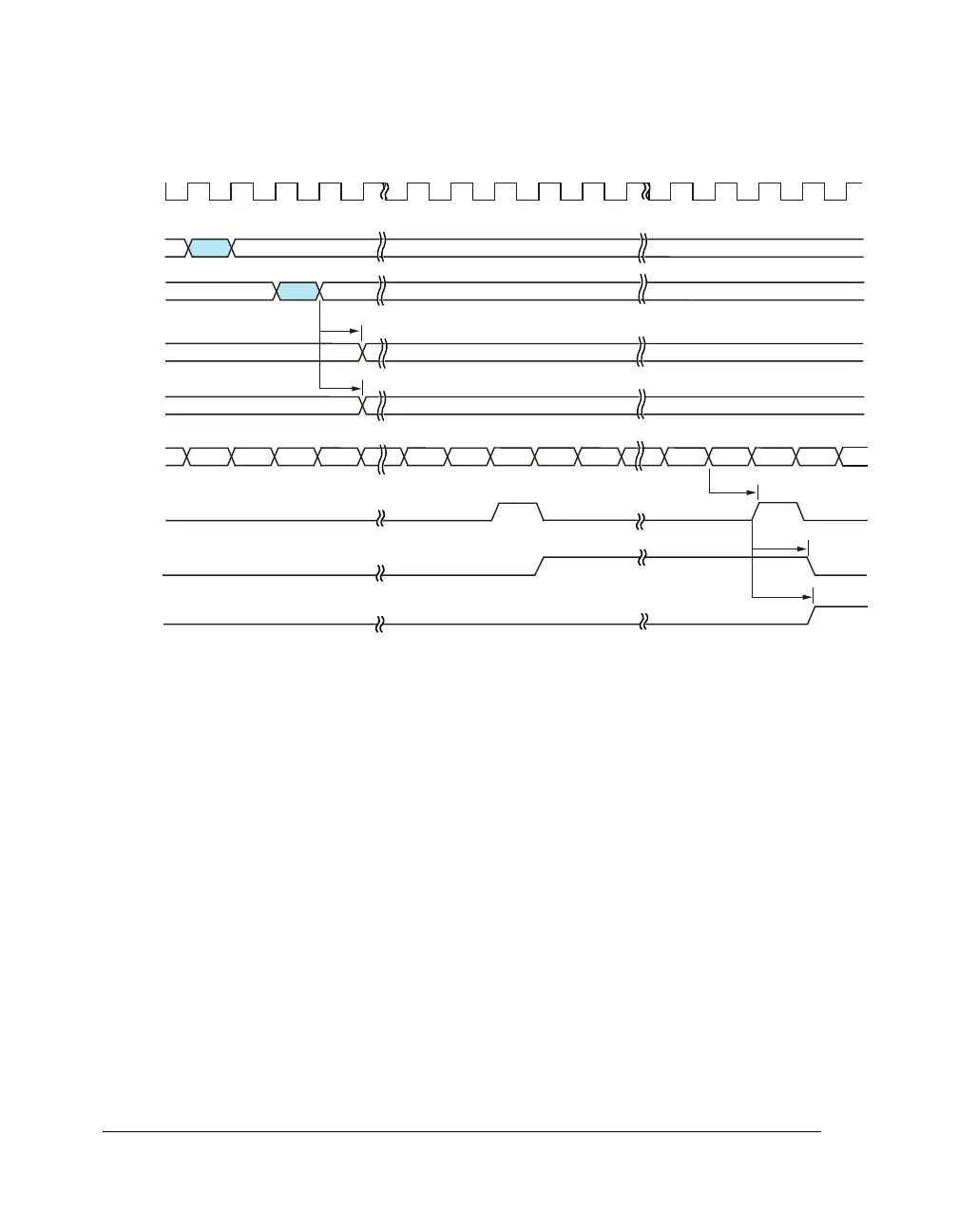

Figure 16-3. PWM_OUT Timing

PCLK

W_BUF

P_BUF

W

COUNTER

X

W - 1

W

X - 1

1 02

cycle

cycle

PERIOD

WIDTH

X = P - W

cycle

cycle

IRQ

cycle

P/2

TIMERx_O

1 02

ZERO

W/2

Loading...

Loading...