Processor Booting

23-20 ADSP-214xx SHARC Processor Hardware Reference

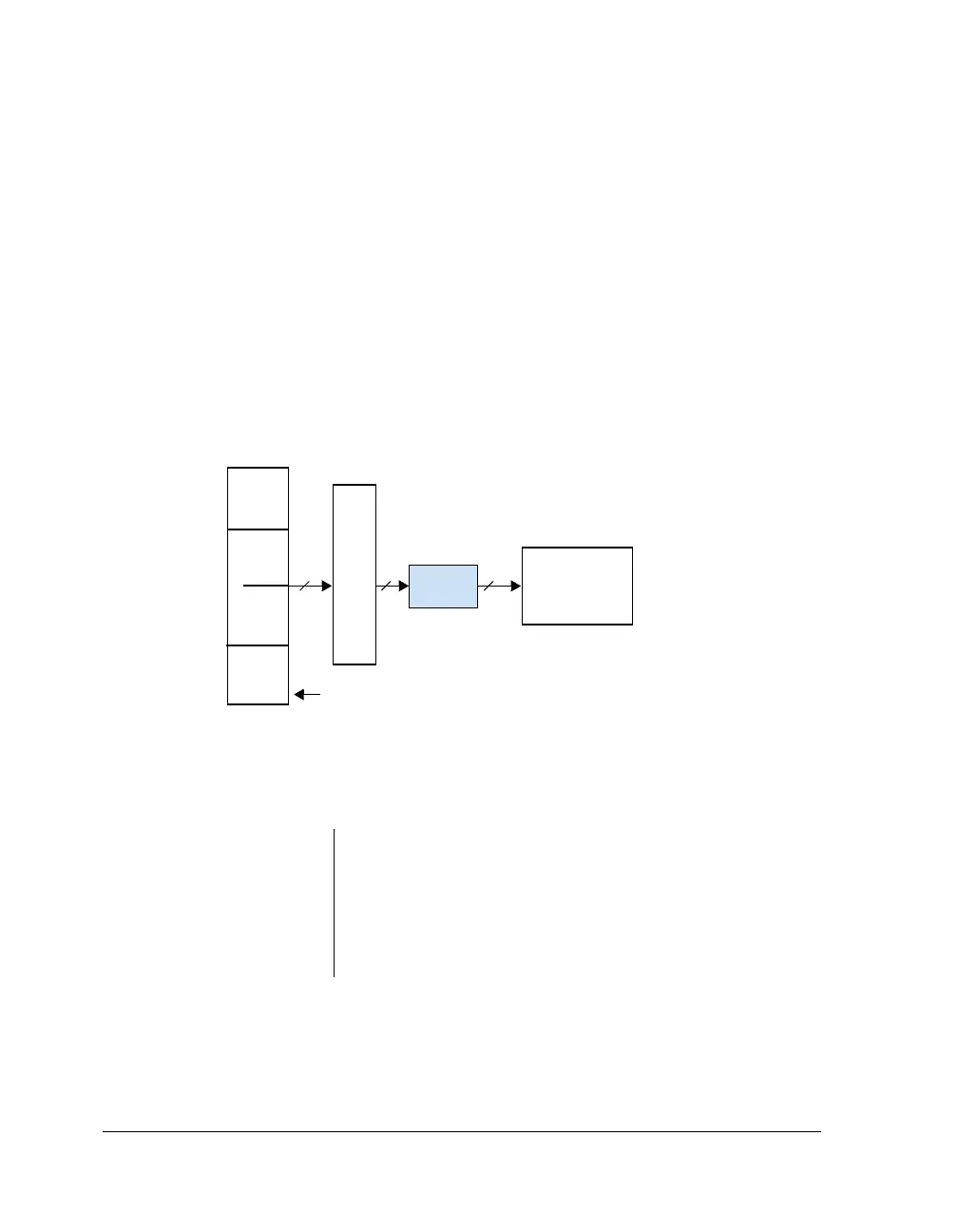

8-Bit SPI Packing

Figure 23-8 shows how an 8-bit SPI host packs 48-bit instructions exe-

cuted at PM addresses PMaddr0 and PMaddr1. For 8-bit hosts, four 8-bit

words pack into the shift register to generate a 32-bit word. The 32-bit

word shifts to internal program memory during the load of the

256-instruction word kernel.

The following code shows a 48-bit instruction executed:

[PMaddr0] 0x112233445566

[PMaddr1] 0x7788AABBCCDD

The 8-bit SPI host packs or prearranges the data as:

The initial boot of the 256-word loader kernel requires an 8-bit host to

transmit 1536 x 8-bit words. The SPI DMA count value of 0x180 is equal

Figure 23-8. 8-Bit SPI Slave Packing

SPI word 1 = 0x66 SPI word 7 = 0xDD

SPI word 2 = 0x55 SPI word 8 = 0xCC

SPI word 3 = 0x44 SPI word 9 = 0xBB

SPI word 4 = 0x33 SPI word 10 = 0xAA

SPI word 5 = 0x22 SPI word 11 = 0x88

SPI word 6= 0x11 SPI word 12= 0x77

SPI_MOSI_I/SPI_MISO_I

8-bit

Word N

RXSPI

DMA

Internal

Memory

32

32

32

8-bit

Word N

8-bit

Word N

8-bit

Word N

RXSR

Loading...

Loading...