ADSP-214xx SHARC Processor Hardware Reference A-245

Registers Reference

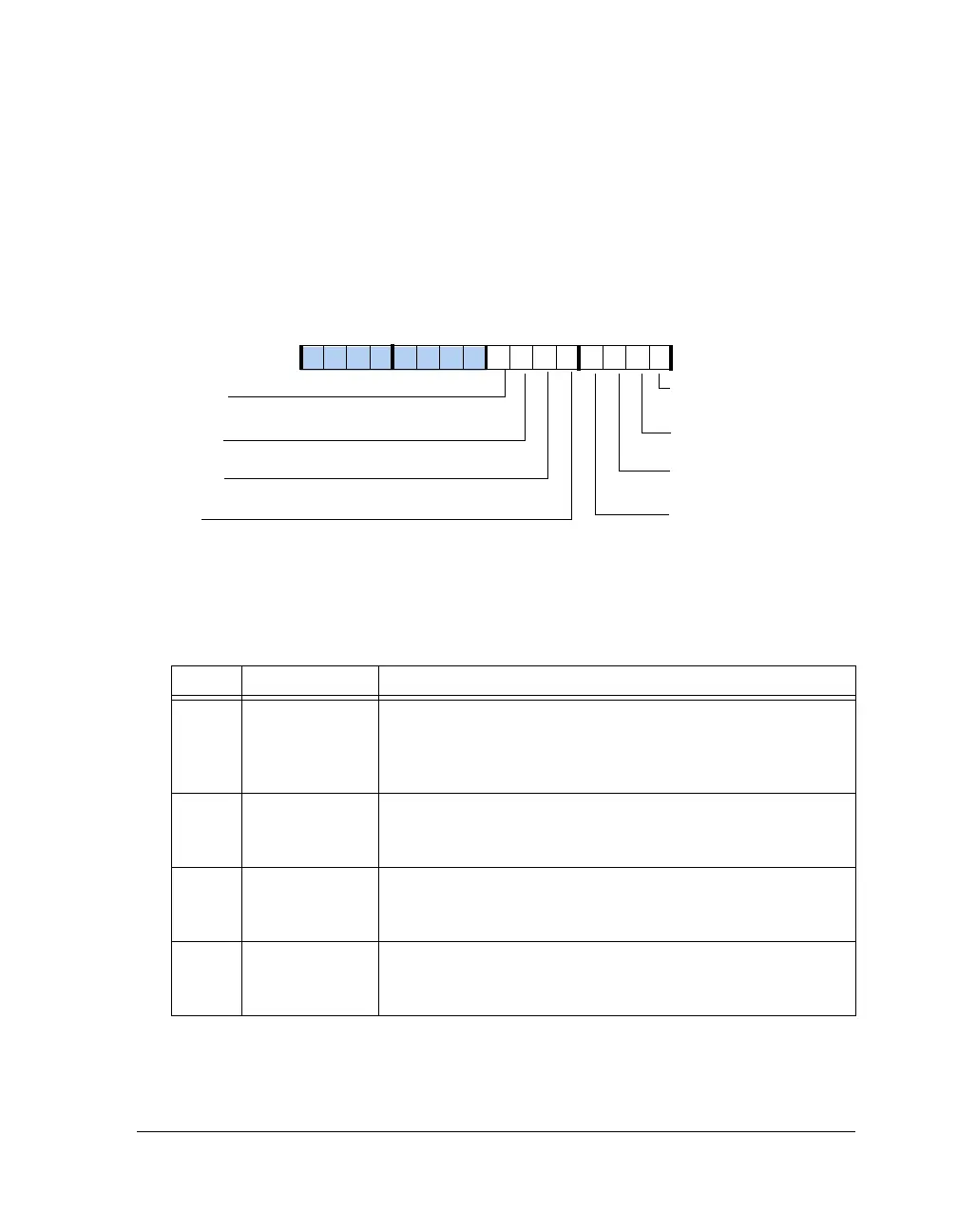

Line Status Register (UART0LSR)

The UART line status register (

UART0LSR) contains UART status informa-

tion as shown in Figure A-137 and described in Table A-128. There is also

a shadow register, UART0LSRSH, that allows programs to read the contents

of the corresponding main register without affecting the status the UART.

Figure A-137. UART0LSR Register

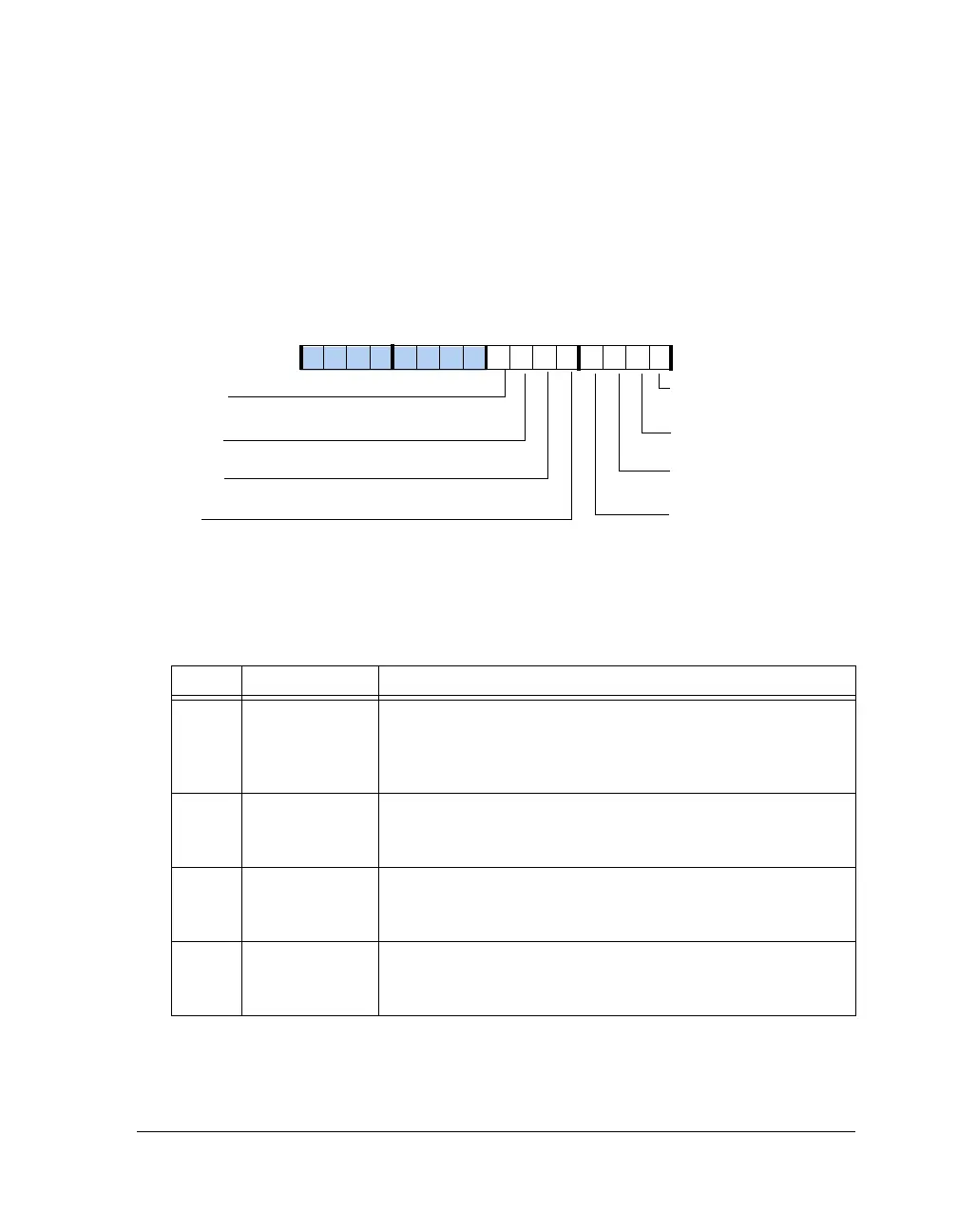

Table A-128. UART0LSR Register Bit Descriptions

Bit Name Description

0 UARTDR Data Ready. This bit is cleared when the UART receive buffer

(UARTxRBR) is read.

0 = No new data

1 = UARTx_RBR holds new data

1

(ROC

1

)

UARTOE Overrun Error.

0 = No overrun

1 = UARTx_RBR overwritten before read

2

(ROC

1

)

UARTPE Parity Error.

0 = No parity error

1 = Parity error

3

(ROC

1

)

UARTFE Framing Error.

0 = No error

1 = Invalid stop bit error

UARTDR

Data Ready

UARTOE

Overrun Error

UARTTHRE

Break Interrupt

UARTBI

UARTPE

Parity Error

UARTFE

UART0_THR Empty

UARTTEMT

TSR and UART0_THR Empty

Framing Error

UARTRX9D

9th Bit

09 837564 2114 12 11 101315

Loading...

Loading...