Features

21-2 ADSP-214xx SHARC Processor Hardware Reference

Features

The TWI is fully compatible with the widely used I

2

C bus standard. It

was designed with a high level of functionality and is compatible with

multimaster, multislave bus configurations. To preserve processor band-

width, the TWI controller can be set up and a transfer initiated with

interrupts only. This allows the processor to service FIFO buffer data

reads and writes. Protocol-related interrupts are optional. The TWI mas-

ter controller includes the features described in the list that follows.

• Simultaneous master and slave operation on multiple device

systems

• Support for multimaster data arbitration

• 7-bit addressing

• 100K bits/second and 400K bits/second data rates

• General call address support

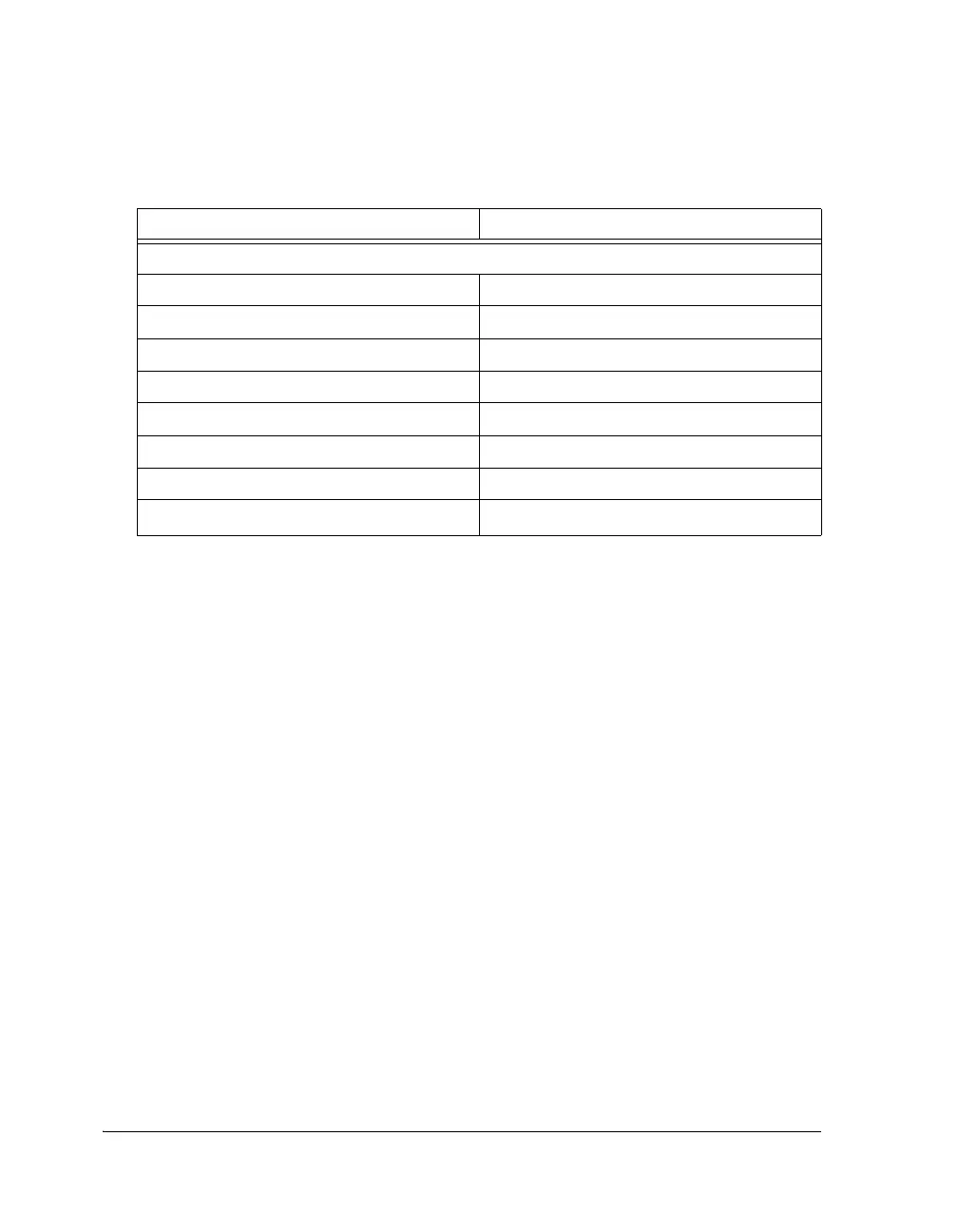

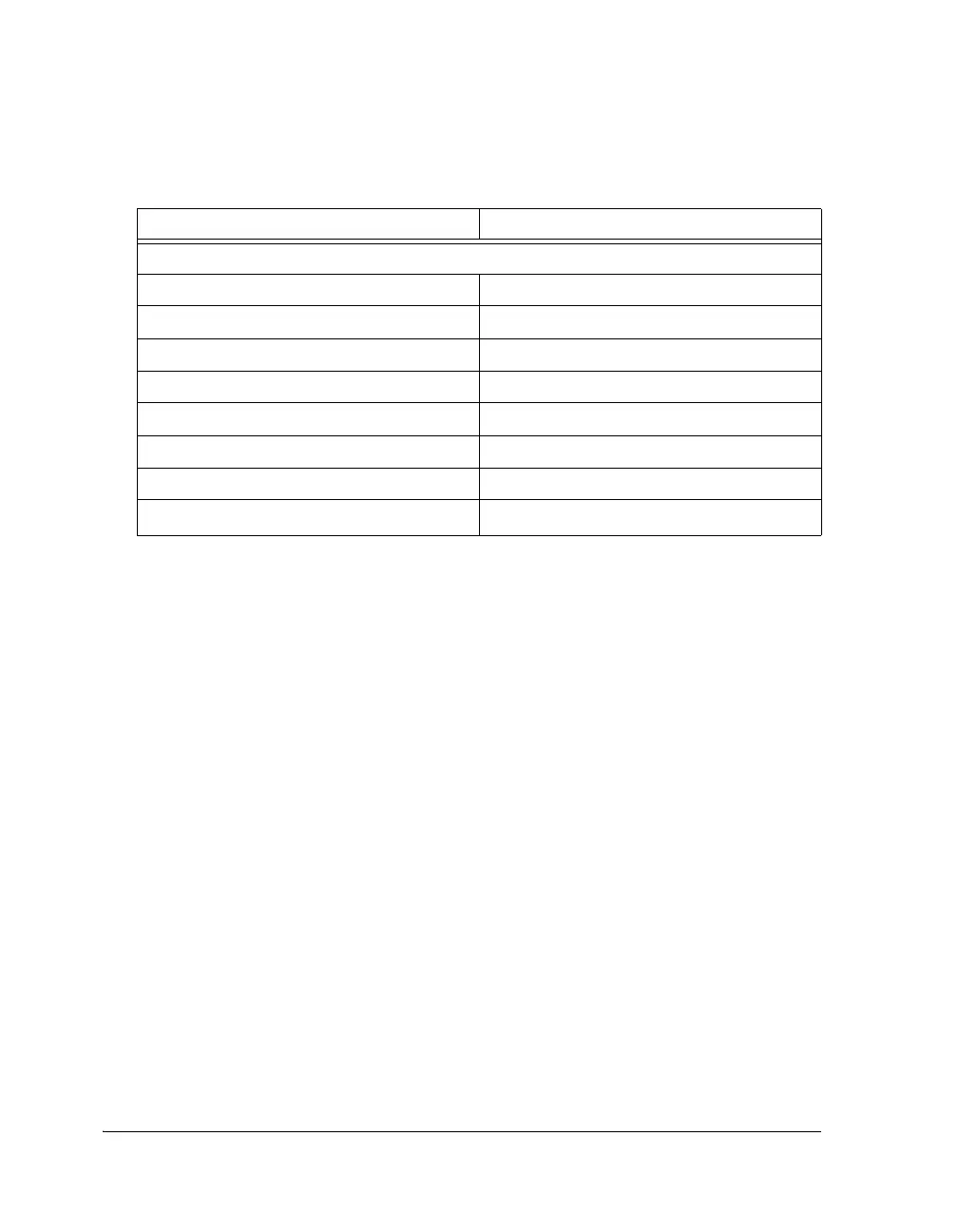

Access Type

Data Buffer Yes

Core Data Access Yes

DMA Data Access No

DMA Channels N/A

DMA Chaining N/A

Boot Capable No

Local Memory No

Clock Operation f

PCLK

Table 21-1. TWI Specifications (Cont’d)

Feature Availability

Loading...

Loading...