ADSP-214xx SHARC Processor Hardware Reference A-99

Registers Reference

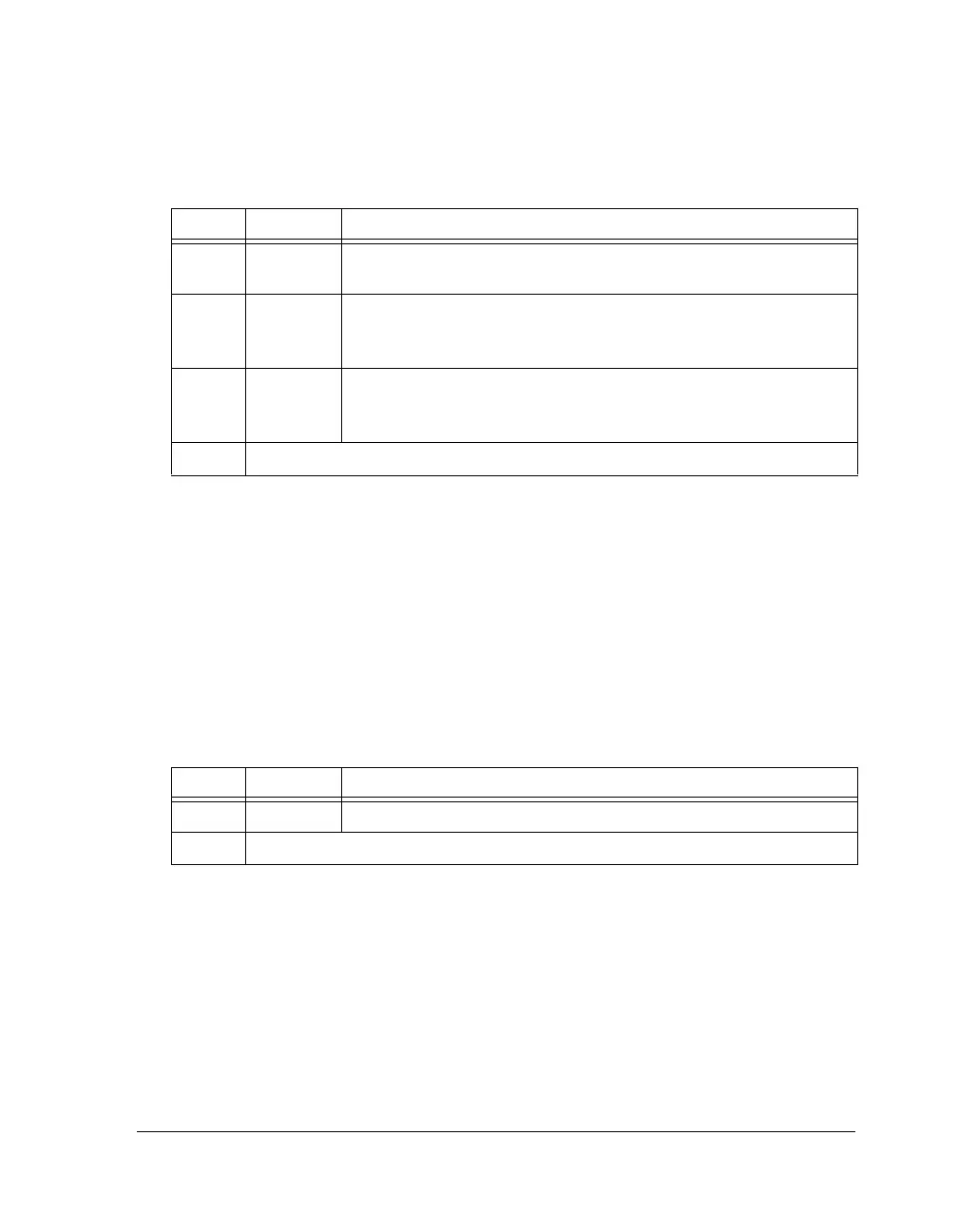

Channel Interrupt Status Register (MLB_CICR)

The channel interrupt status register reflects the channel interrupt status

of the individual logical channels. The channel status update (CSU) bits are

set by hardware when a channel interrupt is generated. The CSU bits are

sticky and can only be reset by software. To clear a particular bit in this

register, software must clear all of the unmasked status bits in the corre-

sponding MLB_CSCRx registers.

MLB Base Registers

The DMA address is constituted by a 5-bit base in the MLB base registers

(for the corresponding channel data type) and a 14-bit offset configured

using the

BCA bits in the MLB_CCBCRx register. The base address registers

and offset registers use round robin arbitration to determine which logical

channel is granted access to the DMA bus.

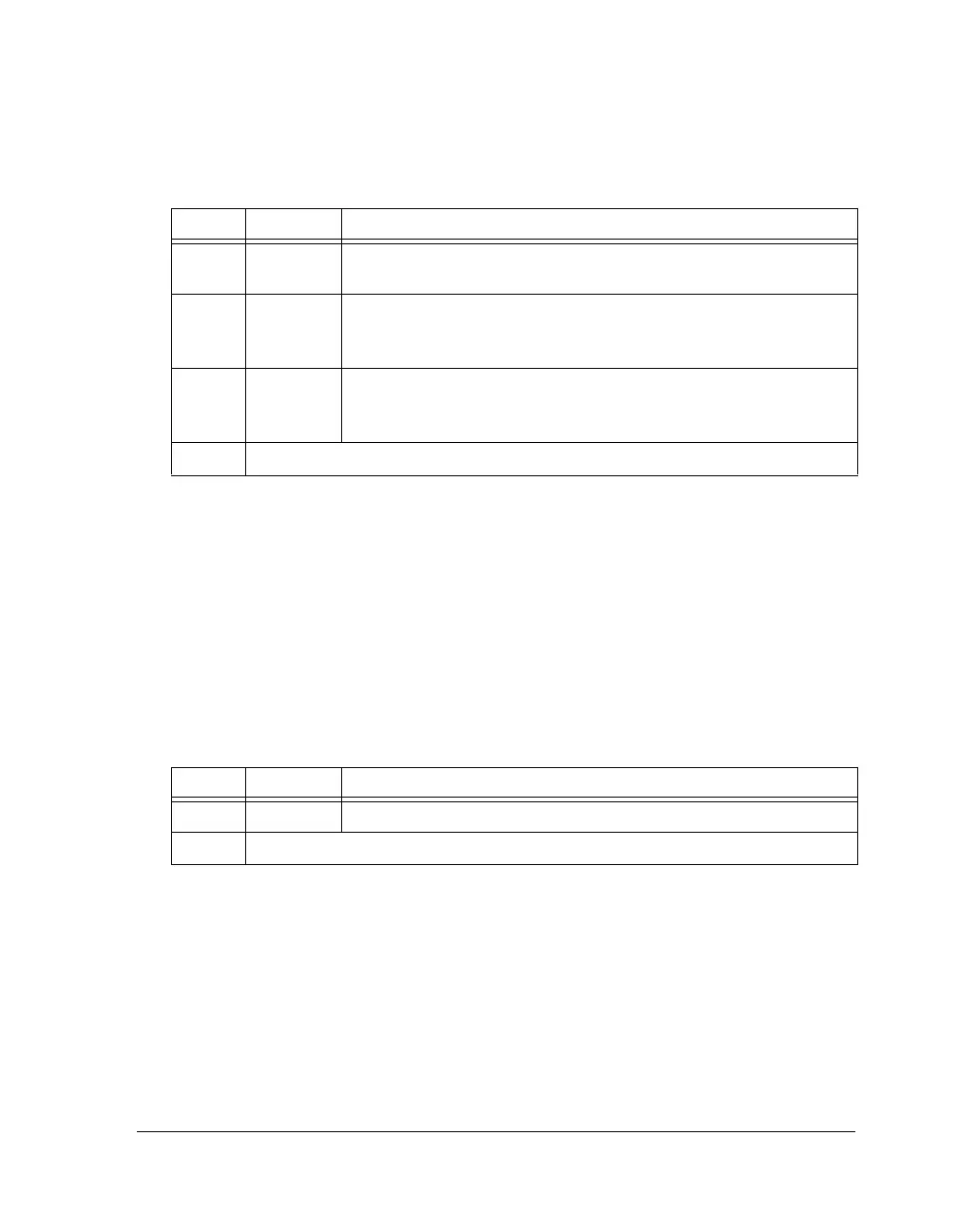

4SMSCSystem Masks Subcommand. When set, this bit masks system interrupts

for MlbSubCmd (0xE6) system command.

5SMMLSystem Masks MLB Lock. When set, this bit masks system interrupts

generated when MLB lock is detected. At reset, MLB lock events are

masked, (SMML = 1).

6SMMUSystem Masks MLB Unlock. When set, this bit masks system interrupts

generated when a MediaLB unlock is detected. At reset, MediaLB unlock

events are masked (SMMU = 1).

31–7 Reserved

Table A-61. MLB_CICR Register Description (RO)

Bit Name Description

30–0 CSU Channel Status Update.

31 Reserved

Table A-60. MLB_SMCR Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...