ADSP-214xx SHARC Processor Hardware Reference A-85

Registers Reference

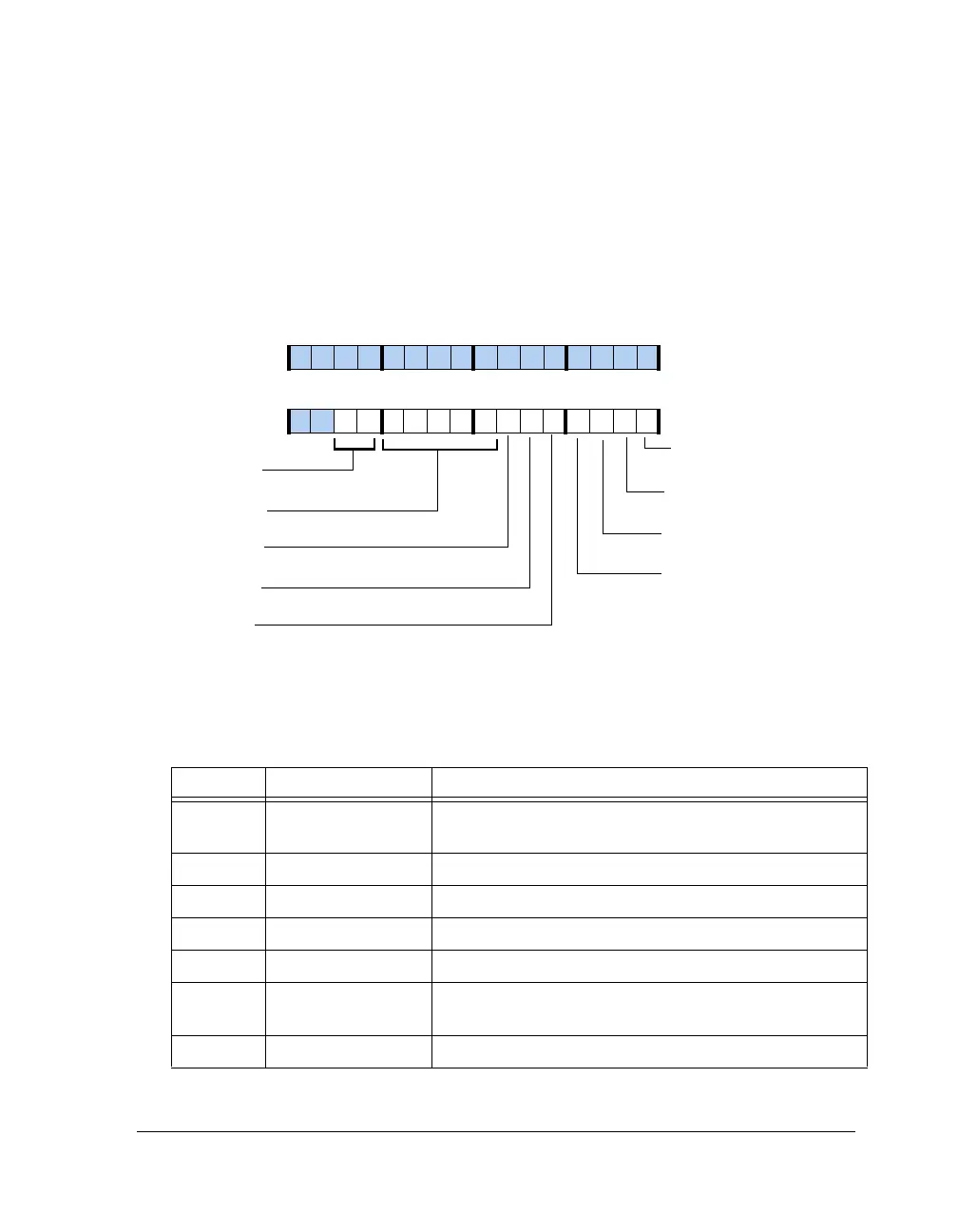

FIR DMA Status Register (FIRDMASTAT)

The information provided by this register, shown in Figure A-38 and

described in Table A-50, are, chain pointer loading, coefficient DMA,

data preload DMA, processing in progress, window complete, all channels

complete.

Figure A-38. FIRDMASTAT Register

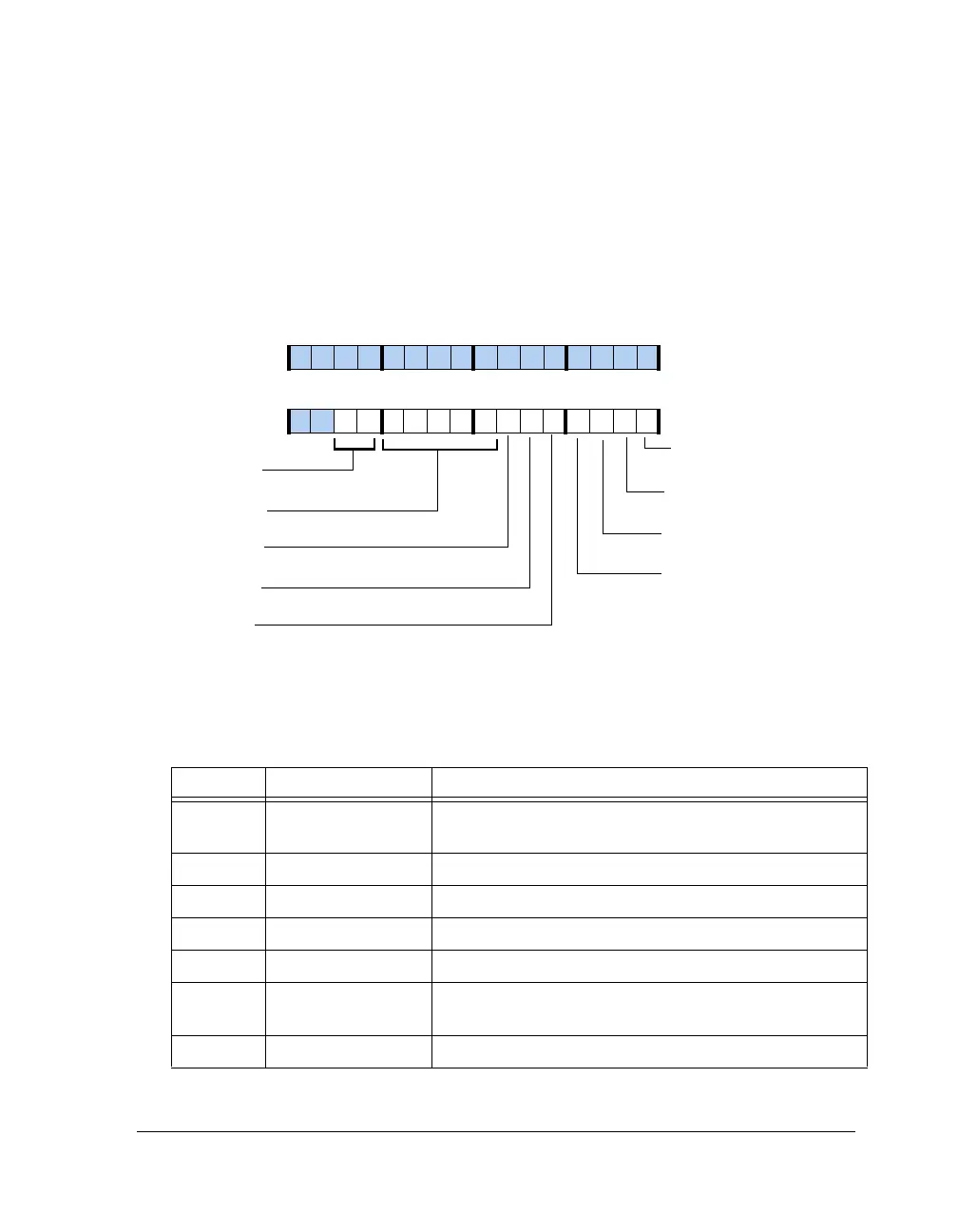

Table A-50. FIRDMASTAT Register Bit Descriptions (RO)

Bits Name Description

0 FIR_DMACPLD Chain Pointer Loading Status. High indicates state machine

in chain pointer load state.

1 FIR_DMACLD Coefficient Loading.

2 FIR_DMADLD Data Preload.

3 FIR_DMAPPGS MAC Processing in Progress.

4 FIR_DMAWRBK Writing Back the Updated Index Registers.

5 (ROC) FIR_DMAWDONE Processing of Current Channel Done. (Sticky – Cleared on

register read).

6 (ROC) FIR_DMAACDONE All Channels Done. (Sticky – Cleared on register read)

FIR_DMACPLD

CURITER (13–12)

Current MAC Iteration

Chain Pointer Load Status

CURCHNL (11–7)

Current Channel

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

FIR_DMACLD

Coefficient Loading

FIR_DMAACDONE

All Channels Done

FIR_DMAPPGS

MAC Processing in

Process

FIR_DMAWDONE

Processing of Current Channel Done

FIR_DMAWRBK

Write Back Updated Index Pointers

FIR_DMADLD

Data Preload

Loading...

Loading...