ADSP-214xx SHARC Processor Hardware Reference 13-3

Sony/Philips Digital Interface

• DAI allows interactions over DAI by serial ports, IDP and/or the

external DAI pins to interface to other S/PDIF devices. This

includes using the receiver to decode incoming biphase encoded

audio streams and passing them via the SPORTs to internal mem-

ory for processing-or using the transmitter to encode audio or

digital data and transfer it to another S/PDIF receiver in the audio

system.

Notice it is important to be familiar with serial digital audio interface

standards IEC-60958, EIAJ CP-340, AES3 and AES11.

Pin Descriptions

Table 13-2 provides descriptions of the pins used for the S/PDIF

transmitter.

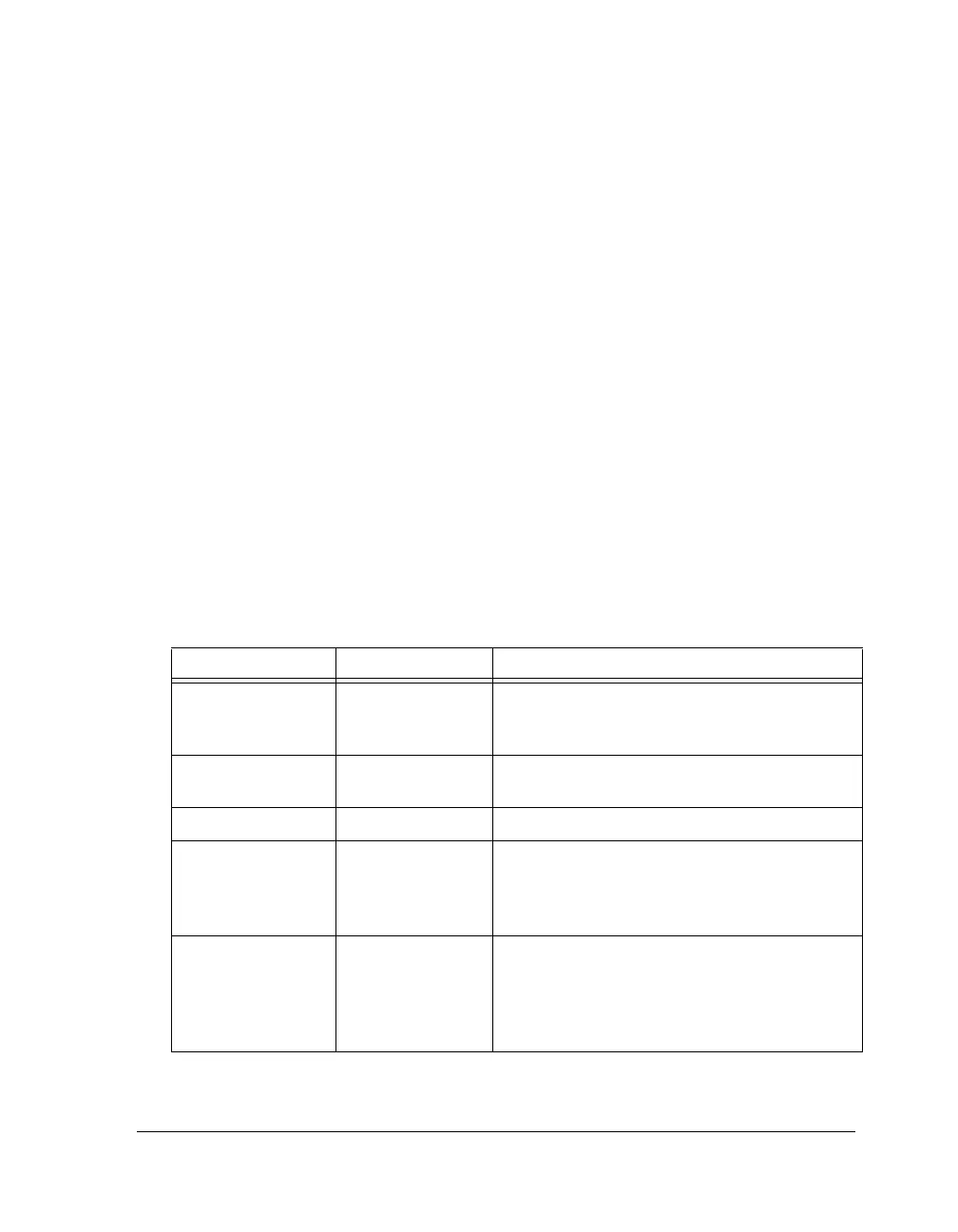

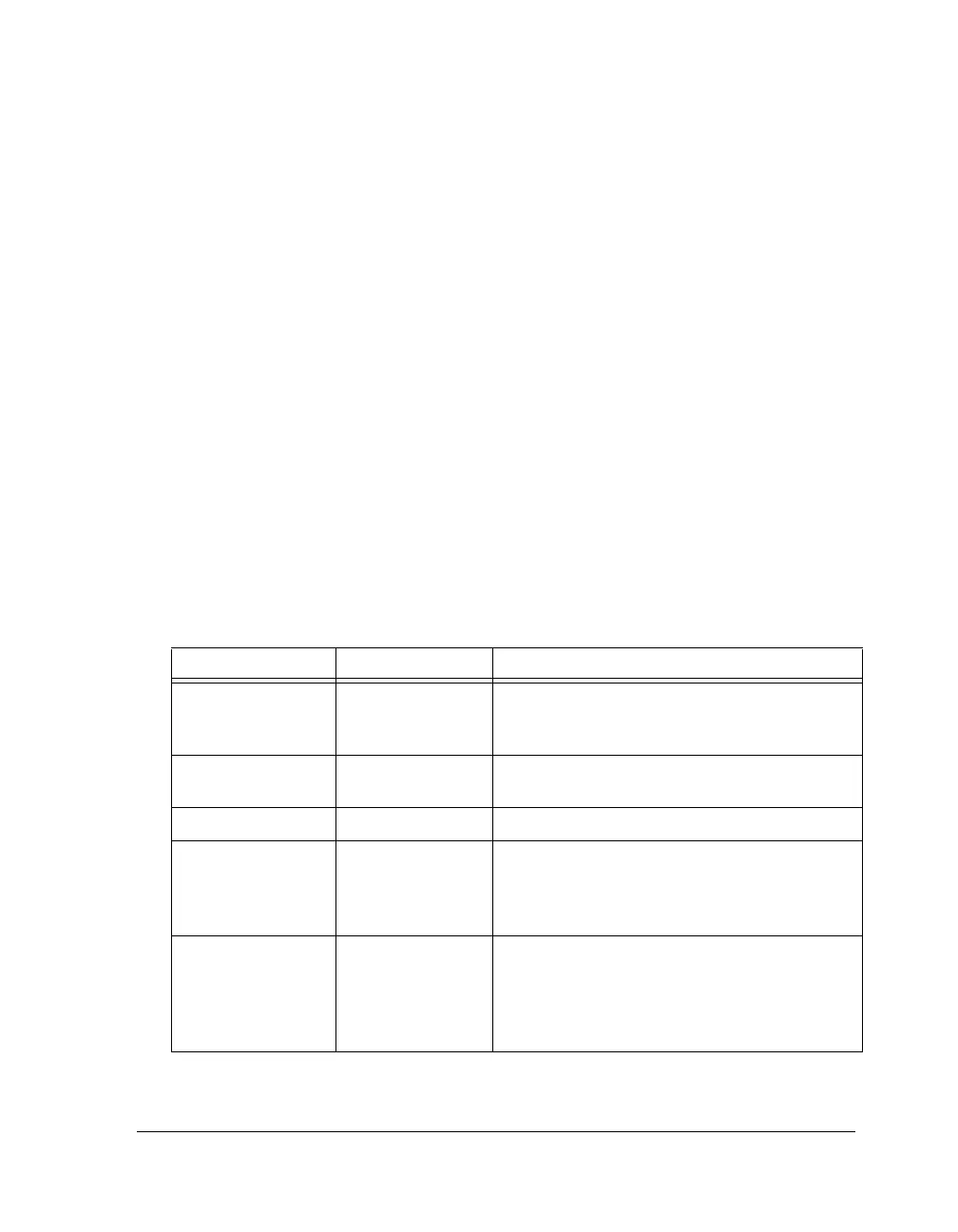

Table 13-2. S/PDIF Transmitter Pin Descriptions

Internal Node I/O Description

DIT_CLK_I Input Serial clock. Controls the rate at which serial data

enters the S/PDIF module. This is typically 64 time

slots.

1

DIT_DAT_I Input Serial Data. The format of the serial data can be

I

2

S, and right- or left-justified.

DIT_FS_I Input Serial Frame Sync.

DIT_HFCLK_I Input Input sampling clock. The over sampling clock

(which is divided down according to the

FREQMULT bit in the transmitter control register

to generate the biphase clock)

DIT_EXTSYNC_I Input External Synchronization. Used for synchronizing

the frame counter. If External synchronization is

enabled (bit 15 of DITCTL is set), Frame counter

resets at rising edge of LRCLK next to the rising

edge of EXT_SYNC_I.

Loading...

Loading...