Peripherals Routed Through the DPI

A-256 ADSP-214xx SHARC Processor Hardware Reference

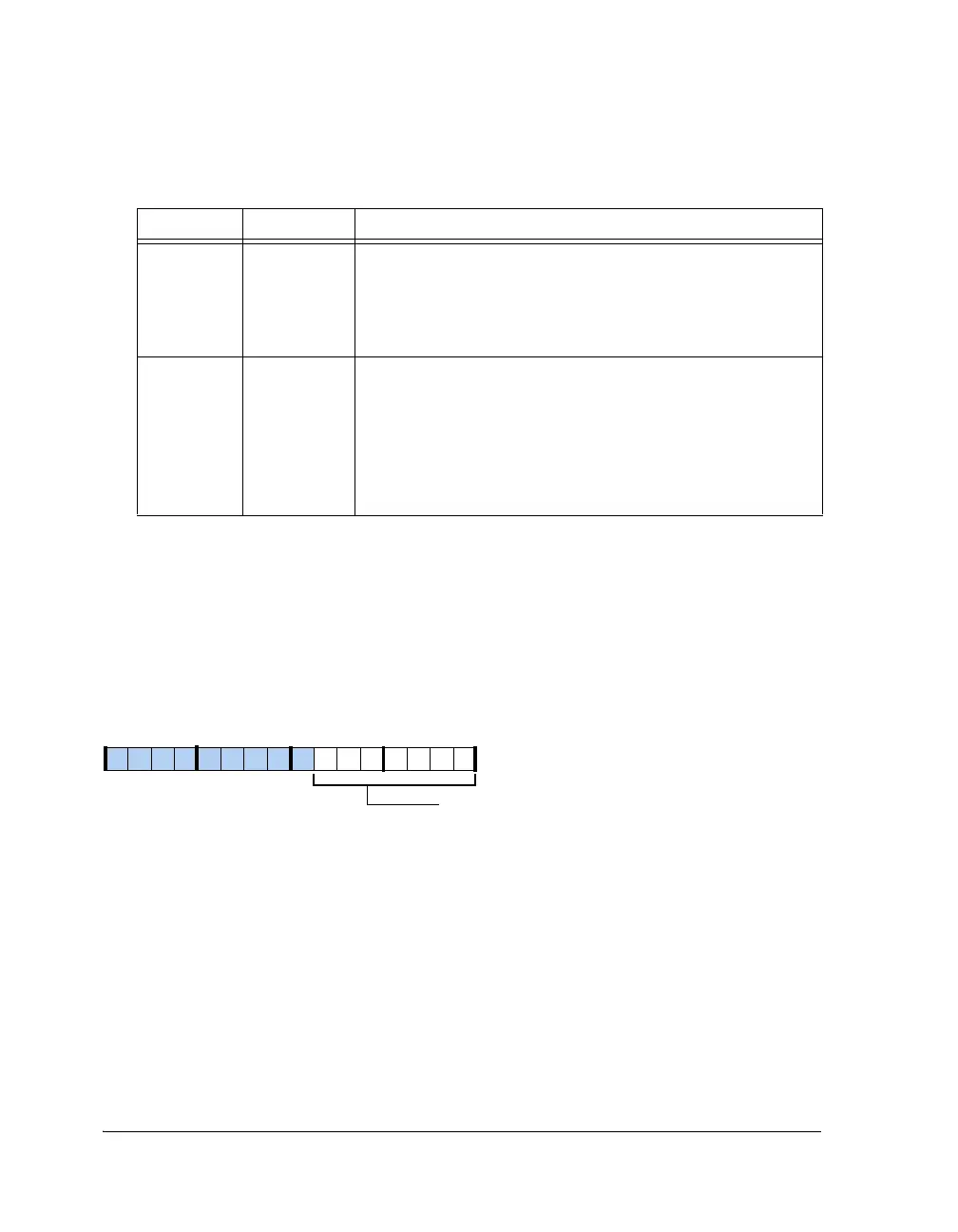

Slave Address Register (TWISADDR)

The TWI slave mode address register (

TWISADDR, shown in Figure A-146)

holds the slave mode address, which is the valid address that the

slave-enabled TWI controller responds to. The TWI controller compares

this value with the received address during the addressing phase of a

transfer.

Slave Status Register (TWISSTAT)

During and at the conclusion of slave mode transfers, the TWI slave mode

status register (shown in Figure A-147) holds information on the current

transfer. Generally slave mode status bits are not associated with the gen-

eration of interrupts. Master mode operation does not affect the slave

mode status bits.

3TWINAK Not Acknowledged.

0 = Slave receive transfer generates an ACK at the conclusion of a

data transfer.

1 = Slave receive transfer generates a data NAK at the conclusion

of a data transfer. The slave is still considered to be addressed.

4TWIGCE General Call Enable. General call address detection is available

only when slave mode is enabled.

0 = General call address matching is not enabled

1 = General call address matching is enabled. Regardless of the

selected address length of slave address, a general call slave receive

transfer is accepted. All status and interrupt source bits associated

with transfers are updated.

Figure A-146. TWISADDR Register (RW)

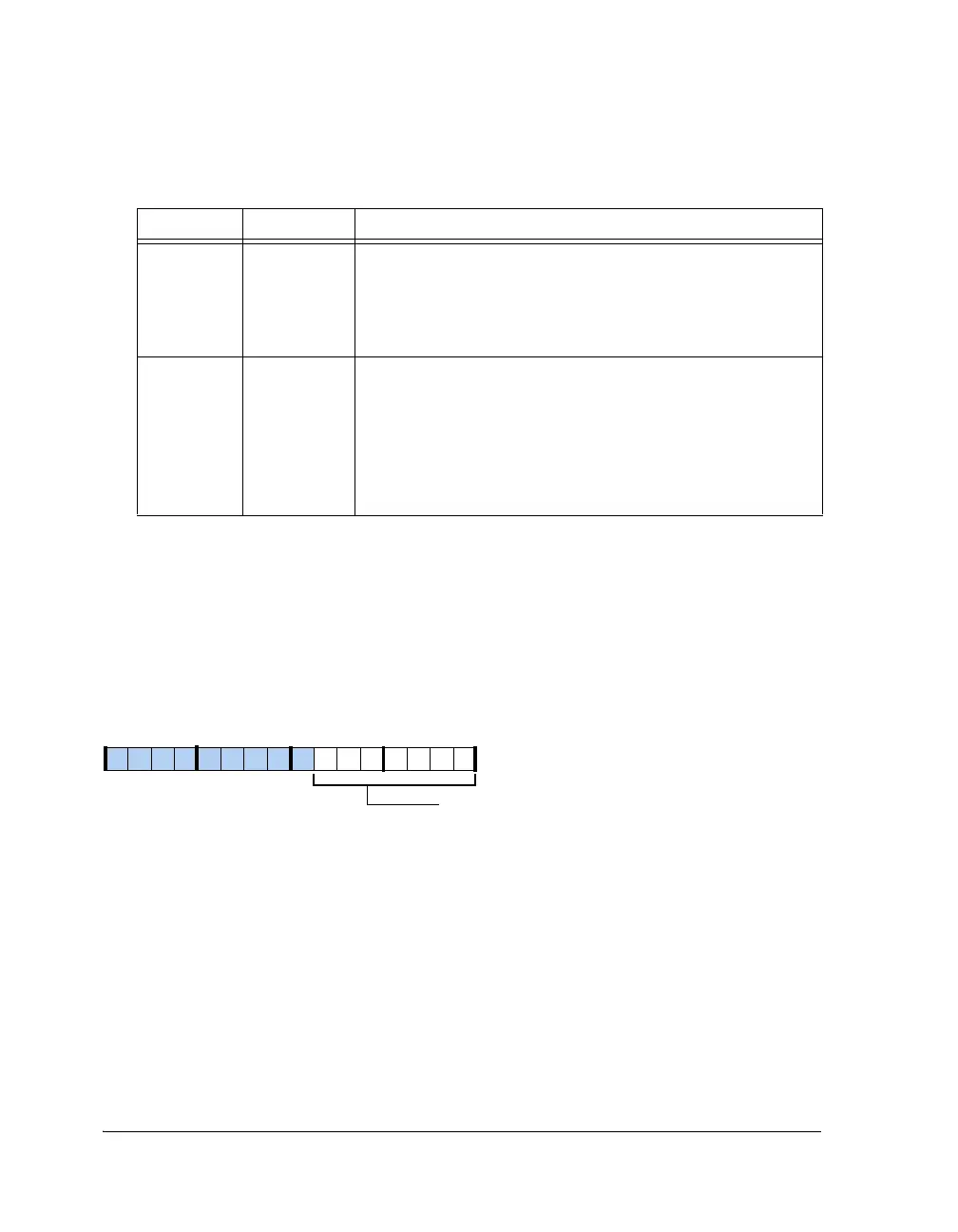

Table A-138. TWISCTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

SADDR (6–0)

Slave Mode Address

09 837564 2114 12 11 101315

Loading...

Loading...