Operating Mode

19-6 ADSP-214xx SHARC Processor Hardware Reference

Operating Mode

The WDT operates in trip count mode as described below.

Trip Count

The WDT contains a software programmable trip counter register that

sets the number of times that the timer can expire before the

WDTRSTO pin

is continually asserted (until the next time hardware reset is applied). The

trip counter is not cleared by the WDT generated reset. This gives soft-

ware the ability to count the number of WDT generated resets using the

CURTRIPVAL bits in the WDTTRIP register.

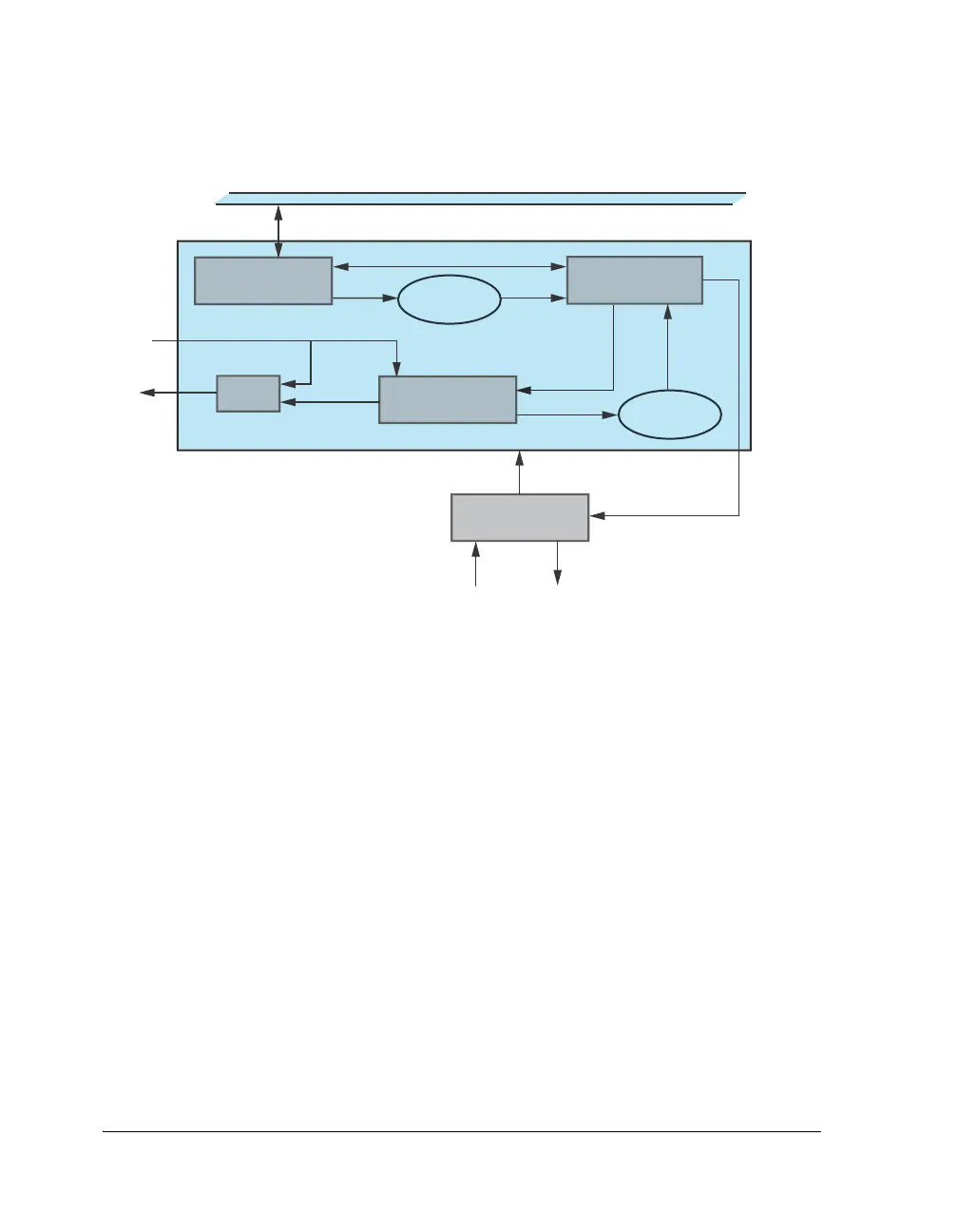

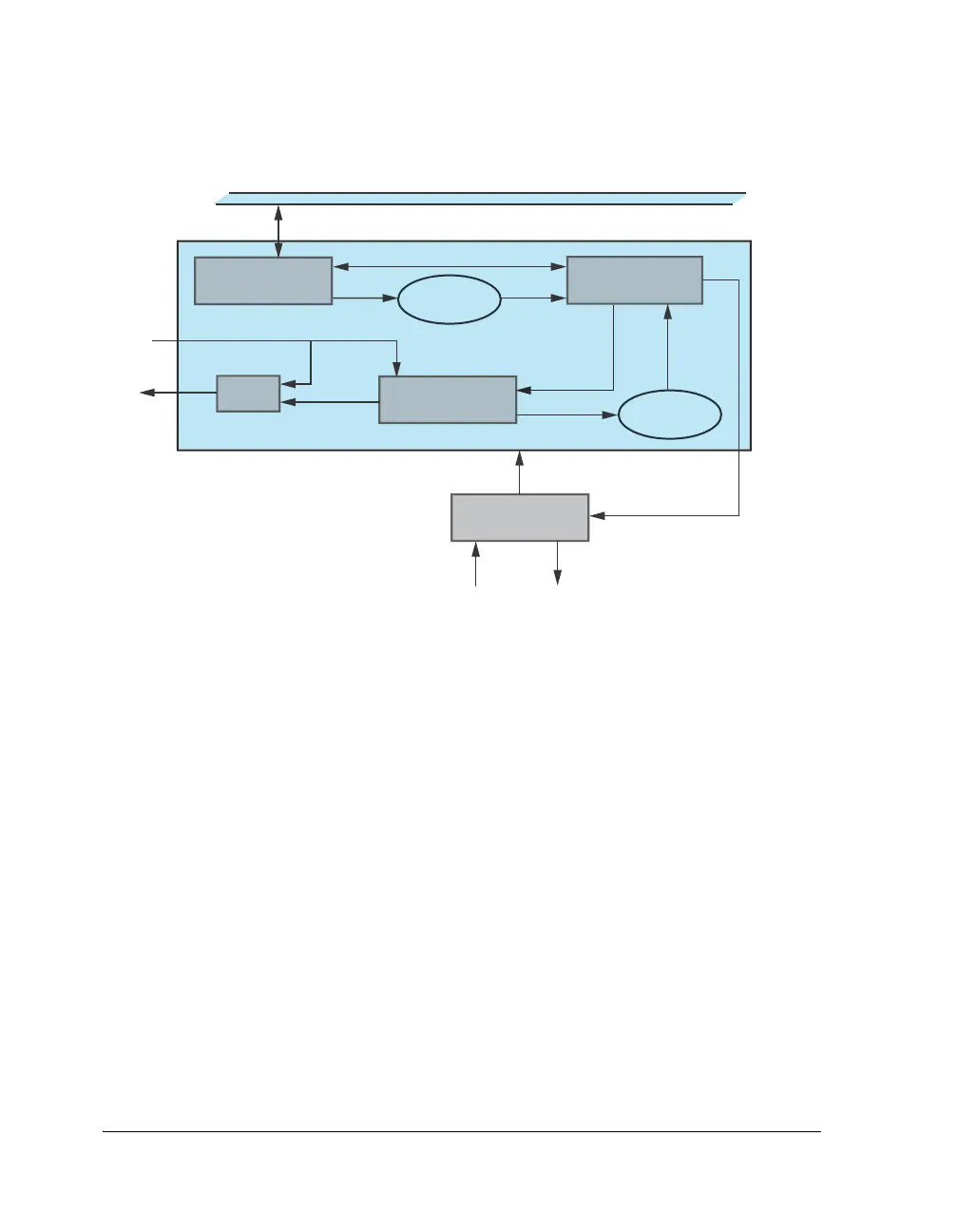

Figure 19-1. Watchdog Timer Block Diagram

PCLK/WDTCLK

SYNC

WDTCLKSEL

DM, PM BUS

WDT REGISTERS

BUS

INTERFACE

COUNTER AND

RESET LOGIC

CLOCK GENERATOR

(Resonator/Oscillator)

PCLK/WDTCLK

SYNC

WDT_CLKOWDT_CLKIN

WDTCLK

AND

WDT_RSTO

WDT RESET

CHIP RESET

WATCH DOG TIMER

Loading...

Loading...