ADSP-214xx SHARC Processor Hardware Reference 15-9

Serial Peripheral Interface Ports

transmitted is irrelevant. A 4-word deep FIFO is included to improve

throughput on the IOD0 bus.

SPI Transaction

An SPI transaction defined start and end depend on whether the device is

configured as a master or a slave, whether

CPHASE mode is selected, and

whether the transfer initiation mode is (

TIMOD) selected. For a master SPI

with CPHASE = 0, a transfer starts when either the TXSPI register is written

or the

RXSPI register is read, depending on the TIMOD selection. At the start

of the transfer, the enabled slave-select outputs are driven active (low).

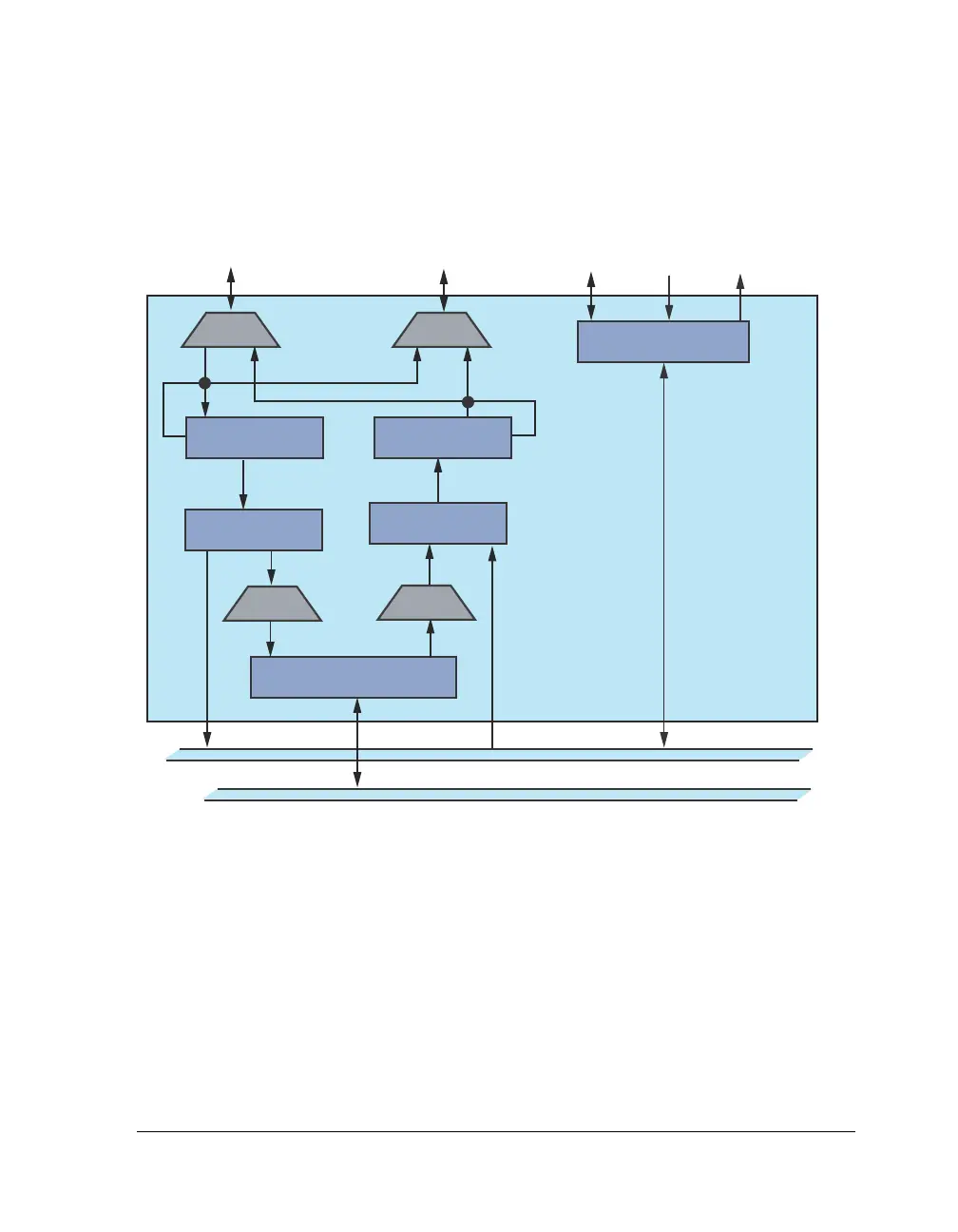

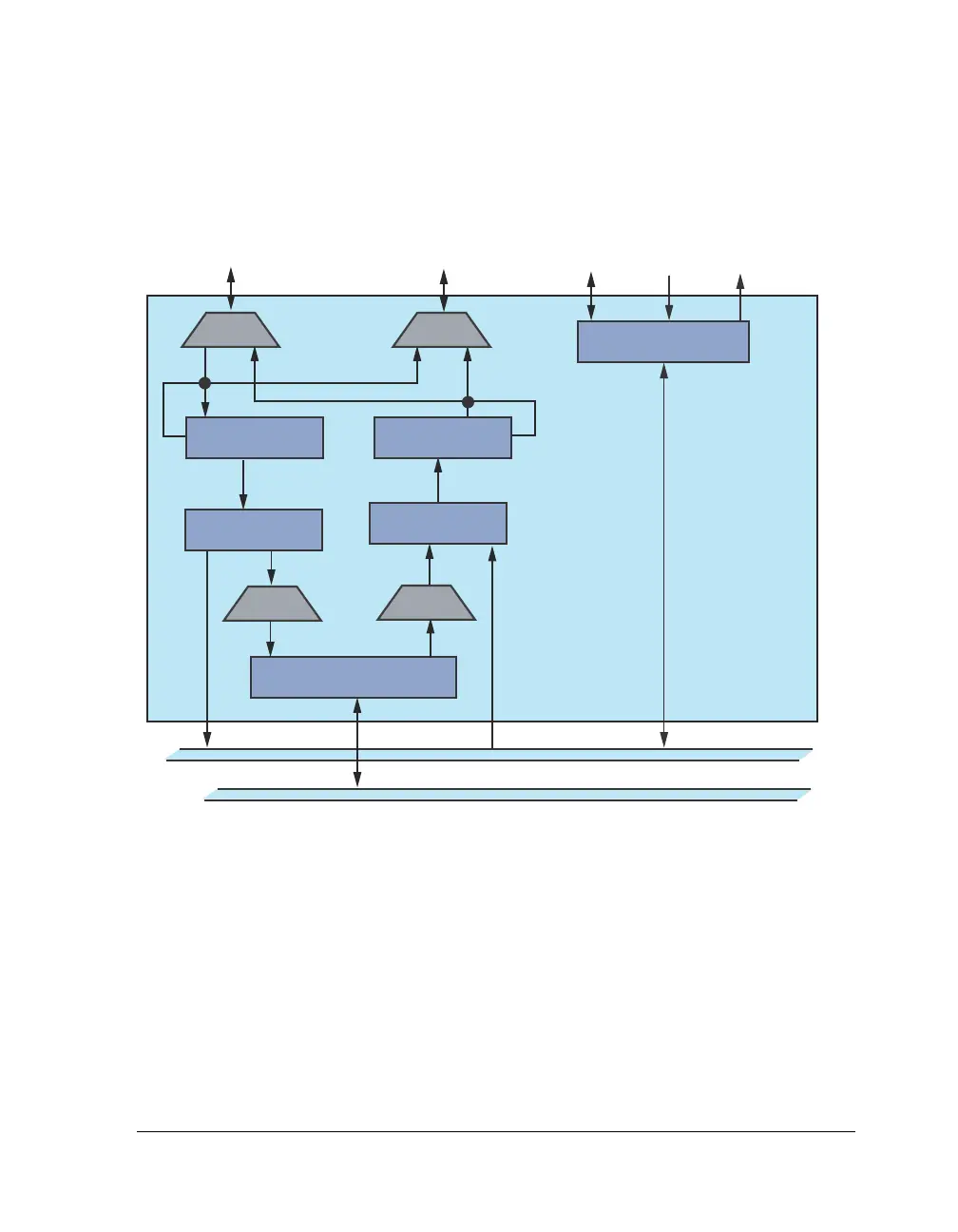

Figure 15-1. SPI Block Diagram

SPIx_MOSI_I/O SPIx_MISO_I/O

SPIx_CLK_I/O SPIx_DS_I

SPIx_FLG_3

-

0_O

DMD, PMD BUSES

IOD0 BUS

RXSR SHIFT REGISTER

8/16/32 BITS

TXSPI REGISTER

1 DEEP

SPI CONTROL/STATUS

RXSPI REGISTER

1 DEEP

DMA FIFO

4 DEEP

TXSR SHIFT REGISTER

8/16/32 BITS

Loading...

Loading...