Operation Modes

10-38 ADSP-214xx SHARC Processor Hardware Reference

for every frame, and therefore emulates I

2

S mode. So it is a hybrid

between multichannel and I

2

S mode.

Clocking Options

In packed mode, the serial ports can either accept an external serial clock

or generate it internally. The ICLK bit in the SPCTL register determines the

selection of these options. For internally-generated serial clocks, the CLK-

DIV

bits in the DIVx register configure the serial clock rate. Finally,

programs can select whether the serial clock edge is used for sampling or

driving serial data and/or frame syncs. This selection is performed using

the CKRE bit in the SPCTL register.

Frame Sync Options

The frame sync period in packed mode is defined as:

FS period = SLEN × number of channels.

The frame sync can be configured in master or slave mode depending on

the

IMFS bit. Moreover the logic level can be changed with the LMFS bit.

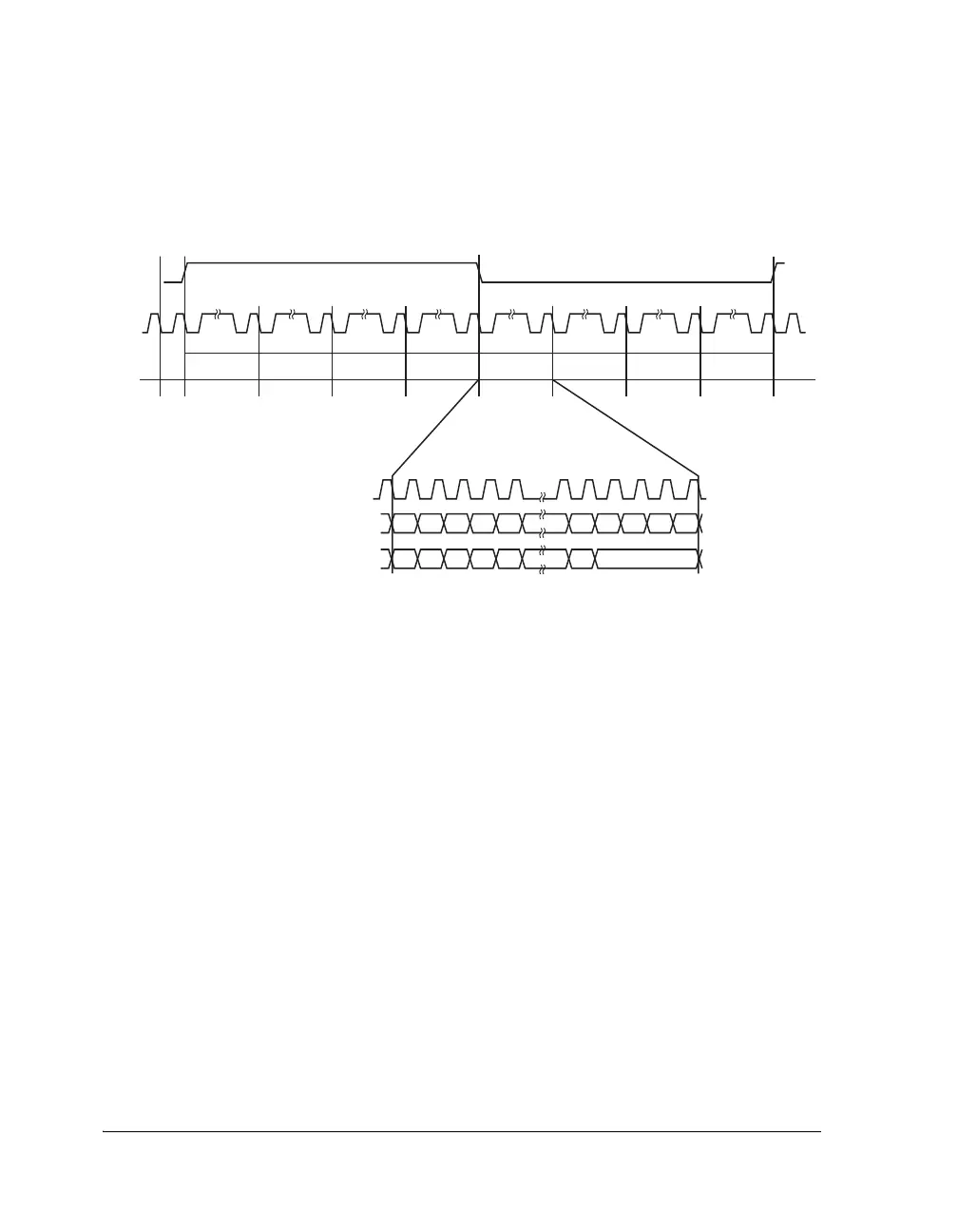

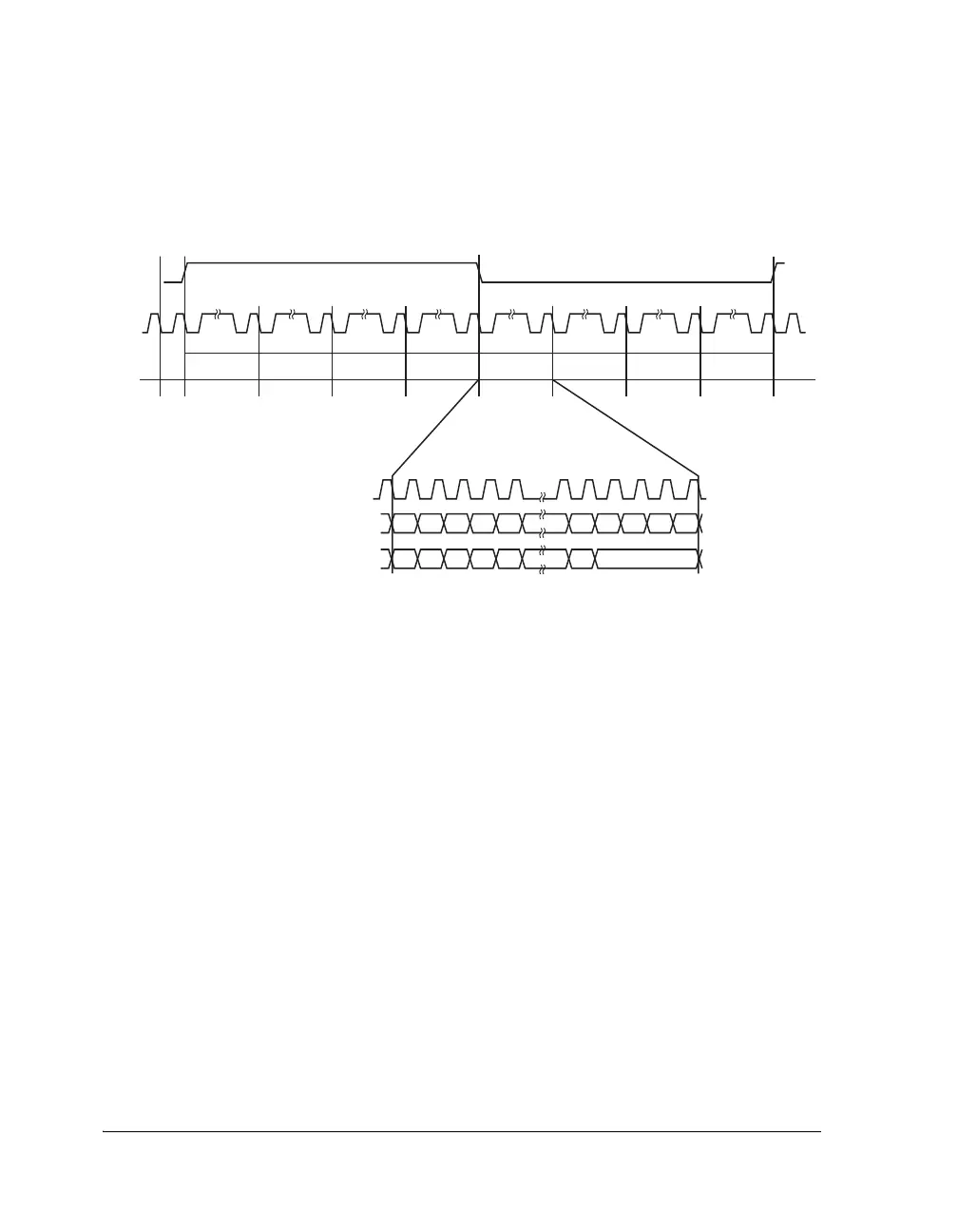

Figure 10-9. Packed Mode 128 Operation

SLOT 1

LEFT 0

SLOT 2

LEFT 1

SLOT 3

LEFT 2

BLANK SLOT

4 SCLK

SLOT 4

RIGHT 0

SLOT 5

RIGHT 1

SLOT 6

RIGHT 2

BLANK SLOT

4 SCLK

DATA

20-BIT DATA

16-BIT DATA

BCLK

BCLK

MSB

–1

MSB

–2

MSB

–3

MSB

–4

MSB

–1

MSB

–2

MSB

–3

MSB

–4

LSB

+4

LSB

+3

LSB

+2

LSB

+1

MSB LSB

LSBMSB

L/RCLK

Loading...

Loading...