Interrupt Priority

B-4 ADSP-214xx SHARC Processor Hardware Reference

Interrupt Priority

The following sections provide descriptions of the programmable inter-

rupts that are used in the processors. These registers allow programs to

substitute the default interrupts for some other interrupt source.

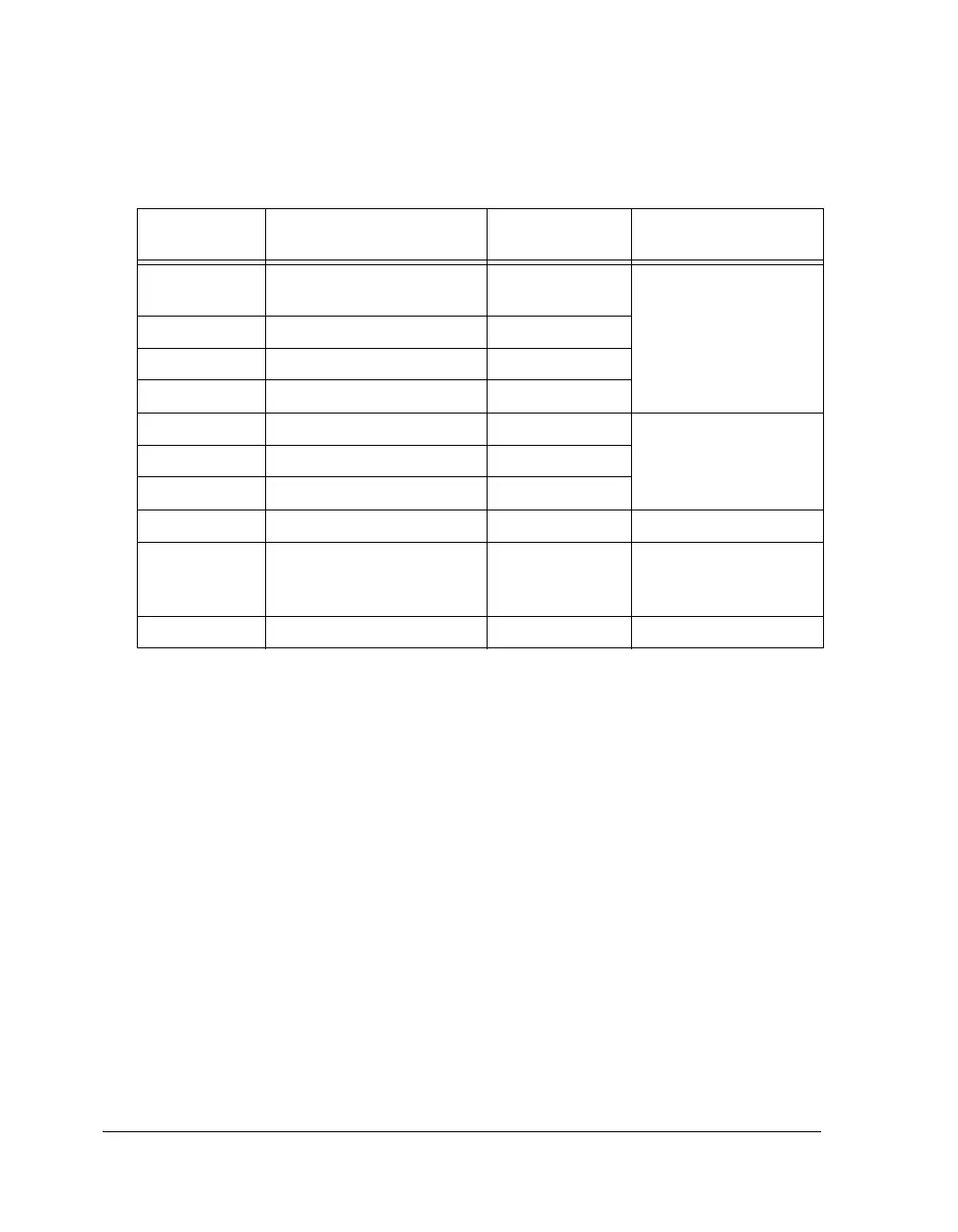

Table B-2 lists the locations to be programmed in the IOP programmable

interrupt control registers (

PICR) to route an IOP interrupt source to a

corresponding processor interrupt location. Note that the shaded area

denotes default routing.

Table B-2 also defines the PICR bits which should be programmed to

select the source for each priority interrupt. Priority programming can be

accomplished by changing the sources for each priority interrupt. For

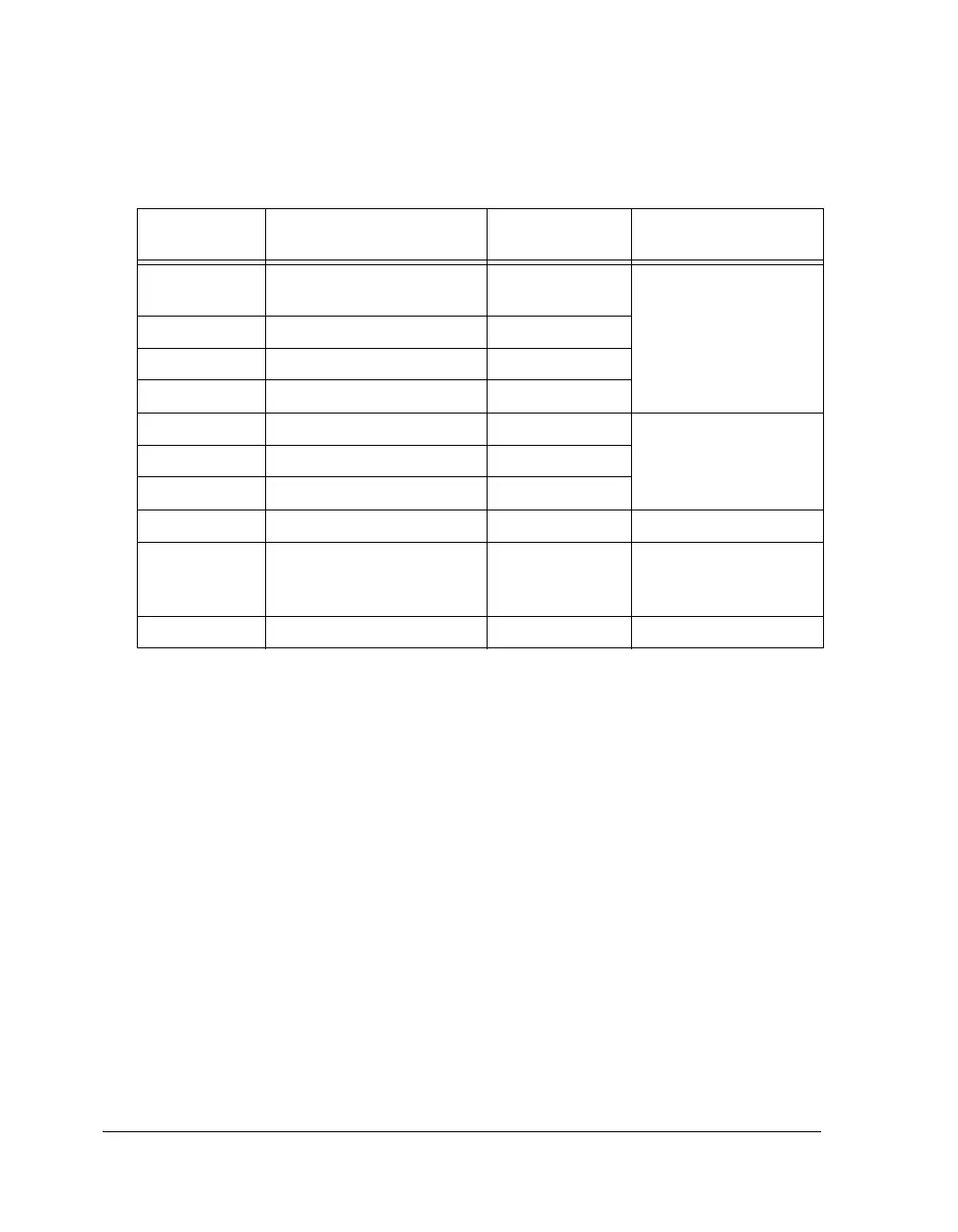

Table B-1. Interrupt Acknowledge Mechanisms

Peripheral Interrupt Source Interrupt Access

Completion

Interrupt Acknowledge

EPDMA1–0 DMA Yes (ADSP-2137x

only)

ISR requires RTI only

MTM DMA No

SPORTs Core/DMA Yes

SPI/SPIB Core/DMA Yes

DAI IDP, SPDIF, ASRC, MISCA No ISR requires

read-only-to-clear

(ROC-bits) and RTI

DPI MISCB No

UART0 Core/DMA No

RTC Core No ROC and RTI

PWM

TWI

Timer1–0

Core No ISR requires write to clear

(W1C) and RTI

MLB Core/DMA No W1C and RTI

Loading...

Loading...