ADSP-214xx SHARC Processor Hardware Reference 10-23

Serial Ports

Mode Selection

The serial port operating mode can be selected via the SPCTLx and the

SPMCTLx/y registers.

1. The operating mode bit 11 (OPMODE) of the SPCTLx register selects

between I

2

S, left-justified, and standard serial/multichannel mode.

2. The operating mode bit 17 (OPMODE) of the SPCTLx register selects

between I

2

S mode and left-justified mode.

3. For packed mode, bit 11 (OPMODE) of the SPCTLx register and bit 0

(MCEA) in the SPMCTLx register enables the A channels and bit 23

(MCEB) in the SPMCTLx register enables the B channels.

4. In multichannel mode, the bit 0 (MCEA) in the SPMCTLx register

enables the A channels and the bit 23 (

MCEB) in the SPMCTLx register

enables the B channels.

5. The

OPMODE bit 17 serves for standard serial mode as late frame sync

bit (

LAFS).

The

SPCTLx register is unique in that the name and functionality of its bits

changes depending on the operation mode selected. In each section that

follows, the bit names associated with the operating modes are described.

Table 10-7 provides values for each of the bits in the SPORT serial

Status

26 DERR_B

27–28 DXS_B

29 DERR_A

30–31 DXS_A

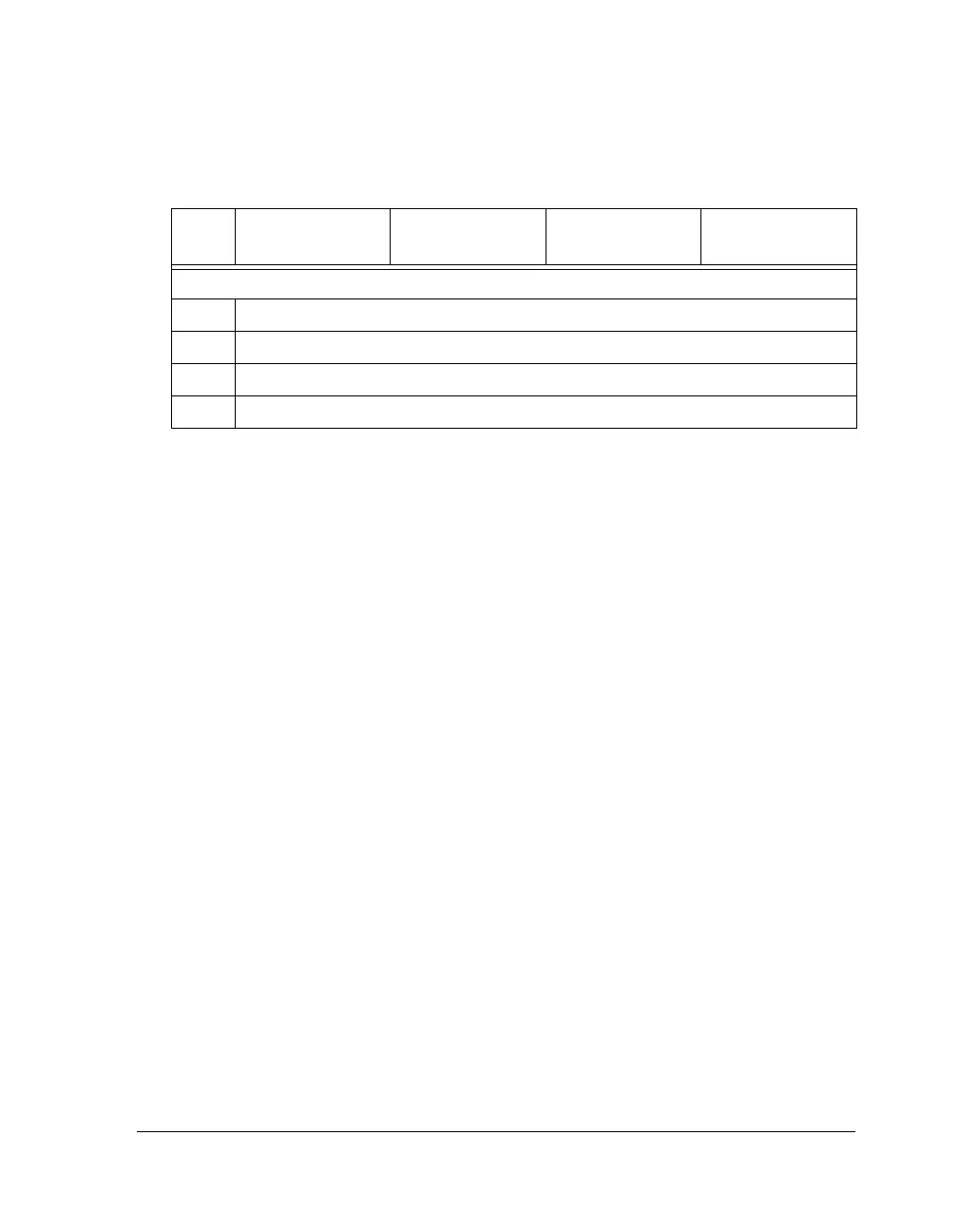

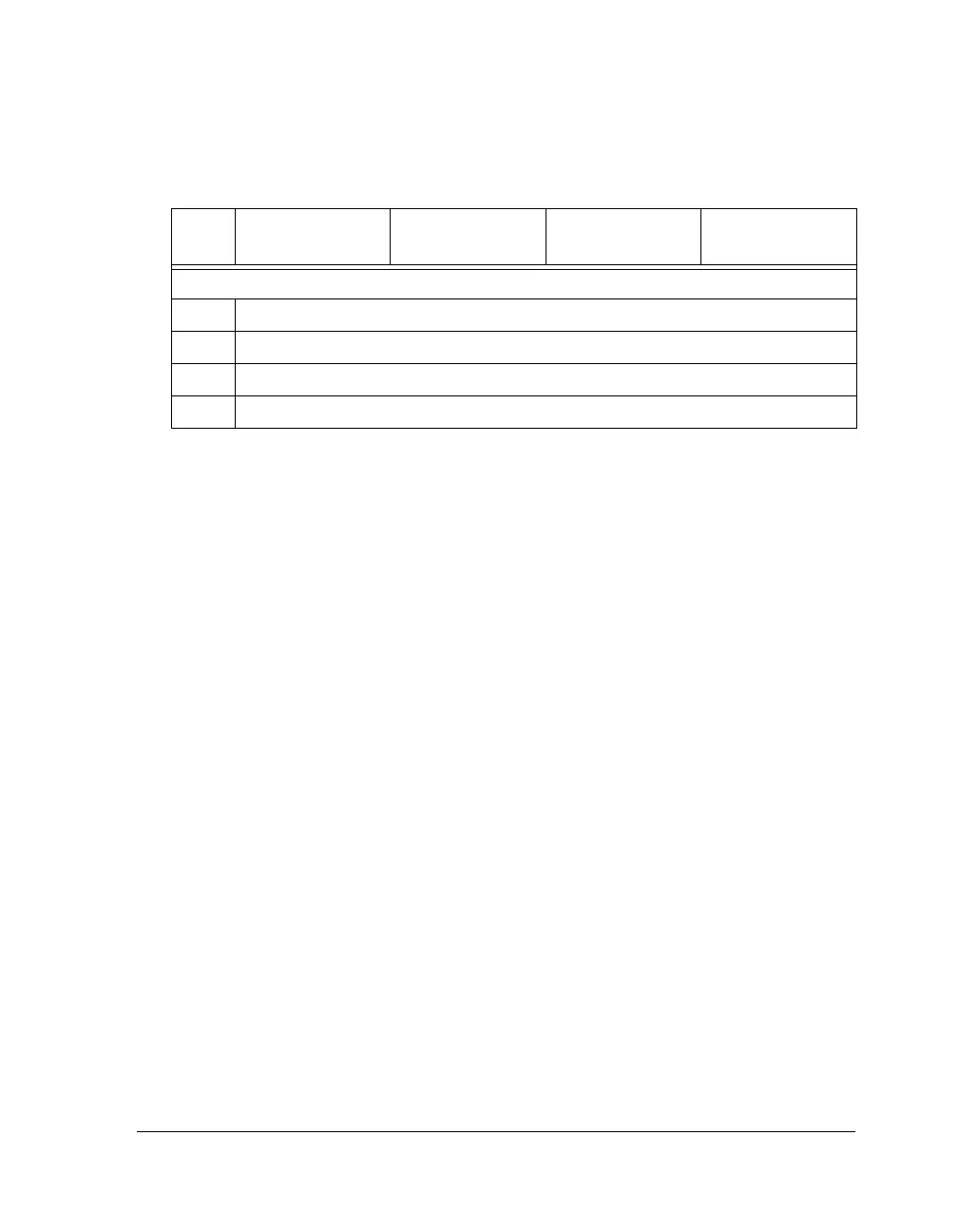

Table 10-6. SPCTLx Control Bit Comparison (Cont’d)

Bit Standard Serial

Mode

I

2

S and

Left-justified Mode

Packed Mode Multichannel Mode

Loading...

Loading...