Functional Description

9-24 ADSP-214xx SHARC Processor Hardware Reference

DAI Routing Capabilities

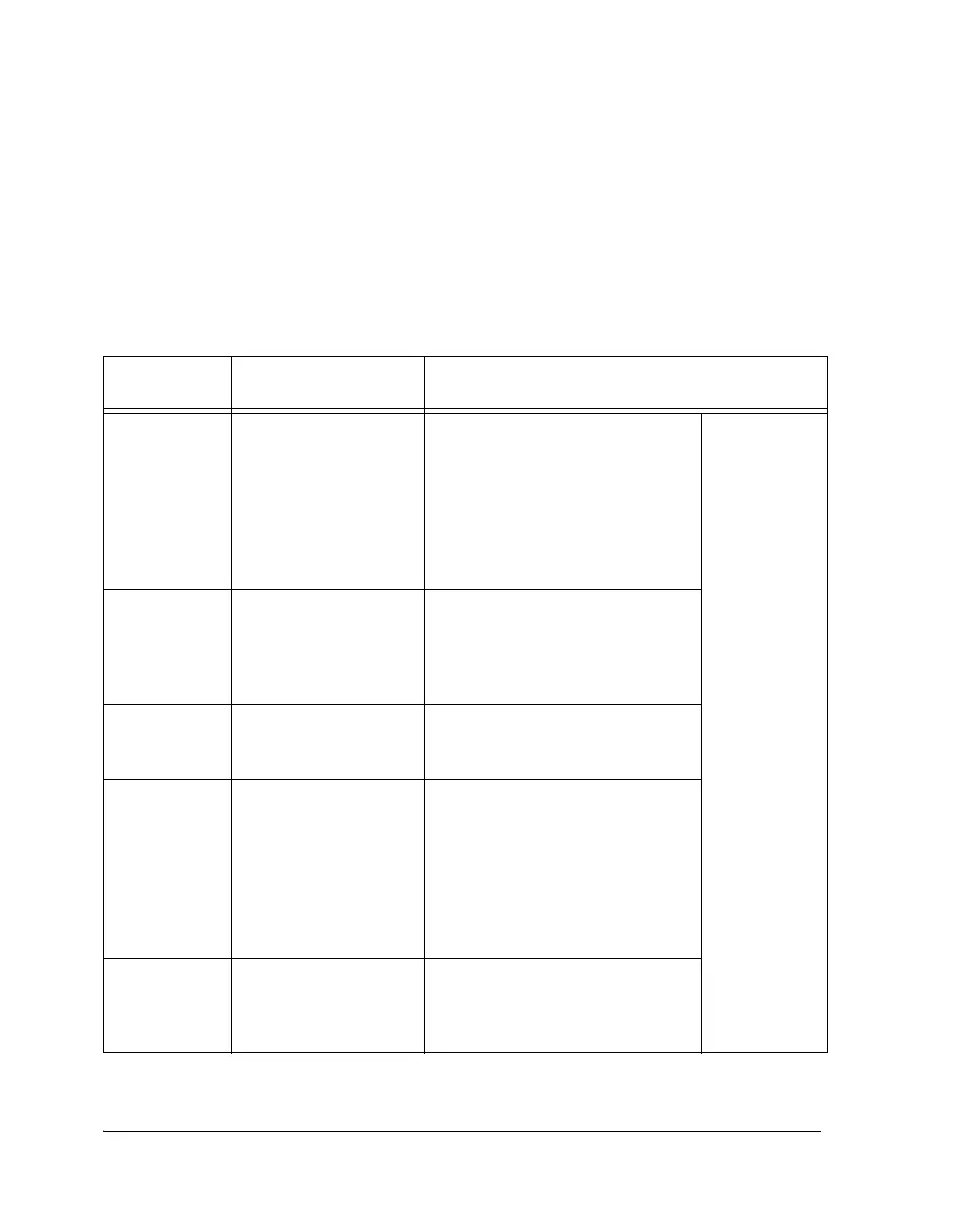

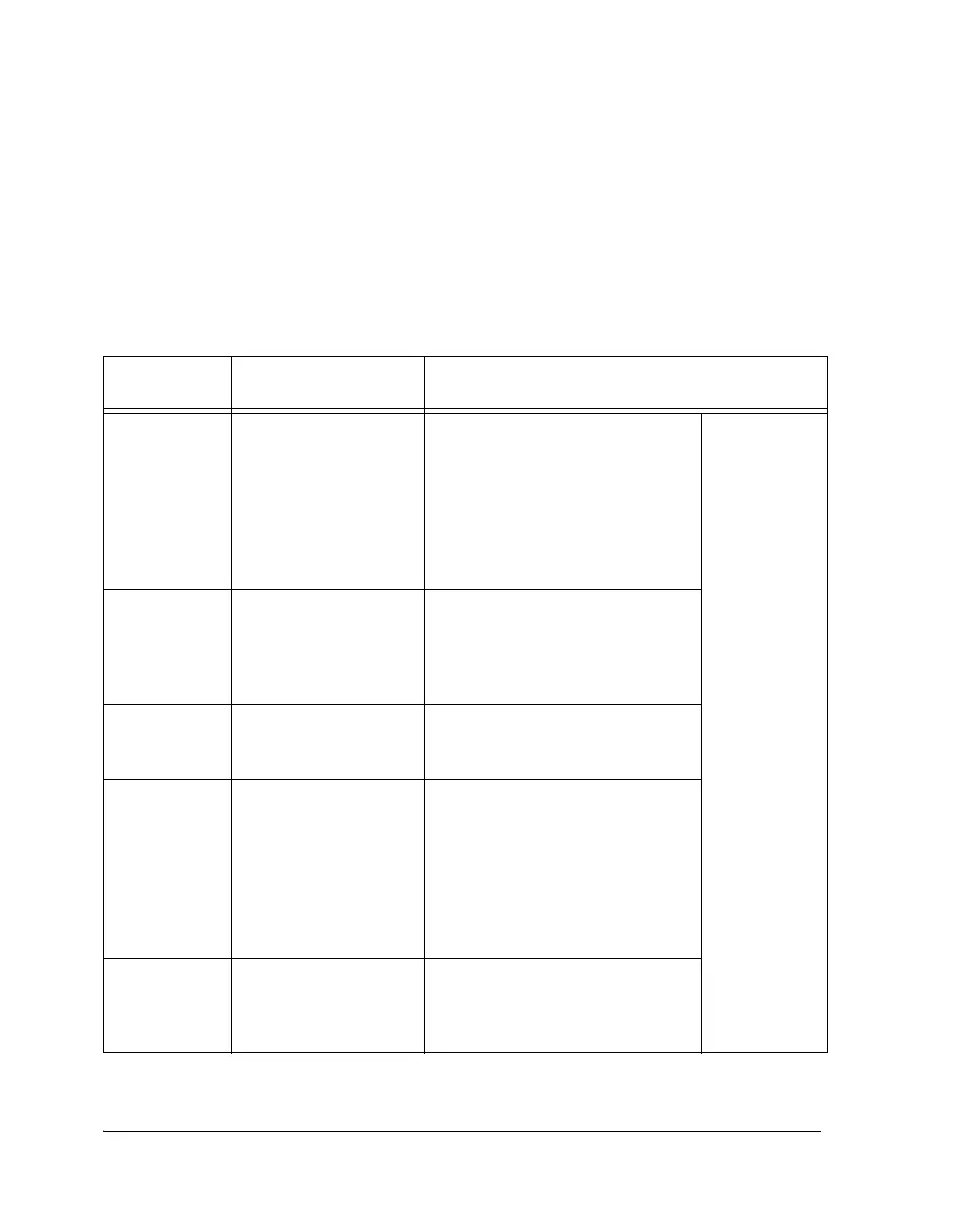

Table 9-1 provides an overview about the different routing capabilities for

the DAI unit. The DAI groups allow routing of specific signals like clocks,

data, frame syncs.

Table 9-4. DAI Routing Capabilities

DAI Group Input (xxxx_I) Output (xxxx_O)

A–Clocks SPORT7–0

SRC3–0

IDP7–0

PCG A, B, C, D (Ext.

clock, Ext. Sync)

S/PDIF-Tx (clock, HF

Clock, ext. sync)

SPDIF-Rx (ext. clock)

SPORT5–0

PCG A, B

S/PDIF Rx (clock, TDM clock)

DAI Pin

Buffer20–1

Logic level high

Logic level low

B–Data SPORT7–0 A, B

SRC3–0 (data, TDM

data)

IDP7–0

S/PDIF Tx/Rx

SPORT7–0 A, B

SRC3–0(data, TDM data)

S/PDIF Tx/Rx

C–Frame Sync SPORT7–0

SRC3–0

IDP7–0

SPORT5–0

PCG A, B

S/PDIF RxX

D–Pin Buffer

Inputs

DAI Pin Buffer 20–1

DAI Pin Buffer 19

Inversion

DAI Pin Buffer 20

Inversion

SPORT7–0A/B (data) SPORT7–0

(clock, FS, TDV, data)

S/PDIF Rx (clock, TDM clock, FS,

data, ext. PLL)

S/PDIF Tx (data, block start)

PDAP (output strobe)

PCG C, D (clock, FS)

SRC3–0 (data)

E–Miscellaneous

Signals

DAI Interrupt 31–22

MISCA5–0

MISCA4 Input Inversion

MISCA5 Input Inversion

SPORT5–0 (FS)

PCG A (clock)

PCG B (clock, FS)

S/PDIF Tx (block start)

Loading...

Loading...