ADSP-214xx SHARC Processor Hardware Reference 16-1

16 PERIPHERAL TIMERS

In addition to the internal core timer, the ADSP-214xx processors contain

identical 32-bit peripheral timers that can be used to interface with exter-

nal devices. Each timer can be individually configured in three operation

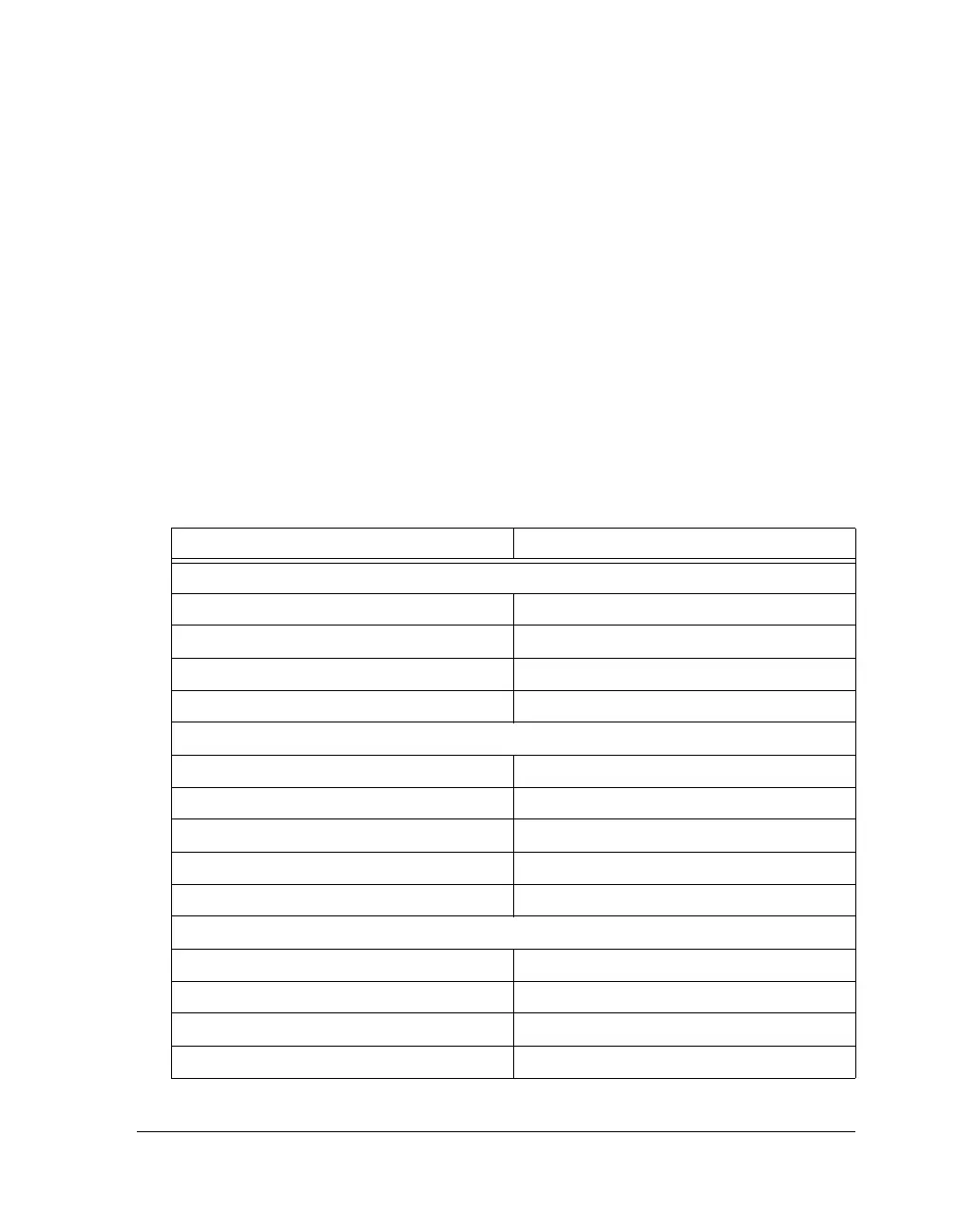

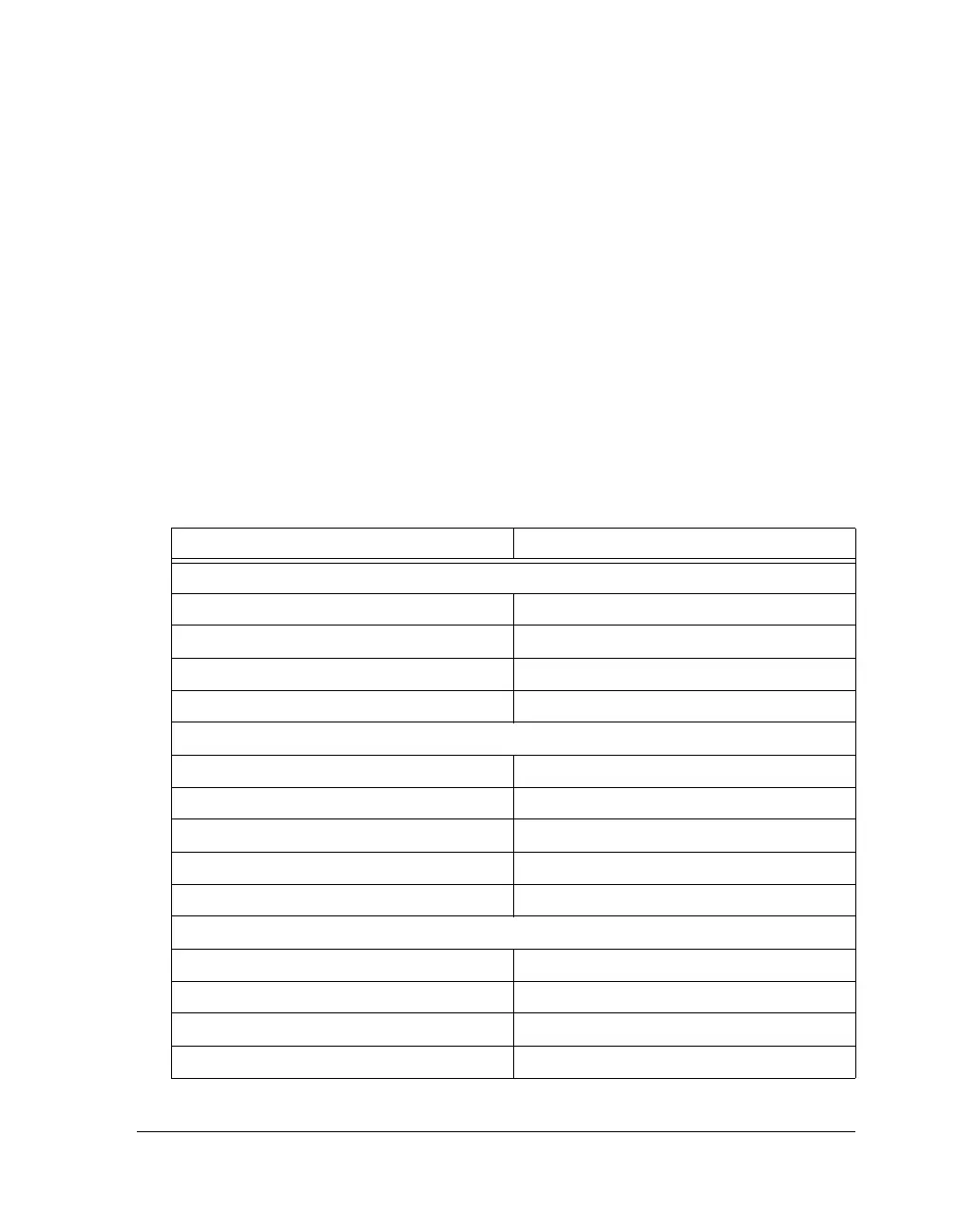

modes. The timers specifications are shown in Table 16-1.

Table 16-1. Timer Specifications

Feature Timer1–0

Connectivity

Multiplexed Pinout No

SRU DPI Required Yes

SRU DPI Default Routing Yes

Interrupt Control Yes

Protocol

Master Capable Yes

Slave Capable Yes

Transmission Simplex N/A

Transmission Half Duplex N/A

Transmission Full Duplex N/A

Access Type

Data Buffer No

Core Data Access N/A

DMA Data Access N/A

DMA Channels N/A

Loading...

Loading...