ADSP-214xx SHARC Processor Hardware Reference 23-3

System Design

SPI DMA Control Register (SPIDMAC). Configures the SPI as receive

DMA which generates an interrupt during boot.

SPI Slave Select Control Register (SPIFLGx). Controls the slave select

configuration for SPI as master during SPI boot.

SPI Baudrate Register (SPIBAUD). Controls the

SPICLK frequency for

master mode during boot.

Processor Reset

After power-up, a RESET is required to place the processor into a known

good state. Table 23-1 shows the differences between a hardware reset

(RESET pin deasserted) or a software reset (setting bit 0 in the SYSCTL regis-

ter) and gives an overview of the different reset methods.

Hardware Reset

All members of the SHARC processor family support the hardware reset

controlled with the RESET pin. The deassertion of this pin enables the PLL

and asserting it resets the PLL. In the time it takes the PLL to acquire lock

(set to 4096 CLKIN cycles), the processor, internal memory, and the

peripherals are held in reset. Upon completion of the 4096 CLKIN cycles,

the chip is brought out of reset. This is indicated on the

RESETOUT pin for

the valid boot modes. For more information, see “Processor Booting” on

page 23-7.

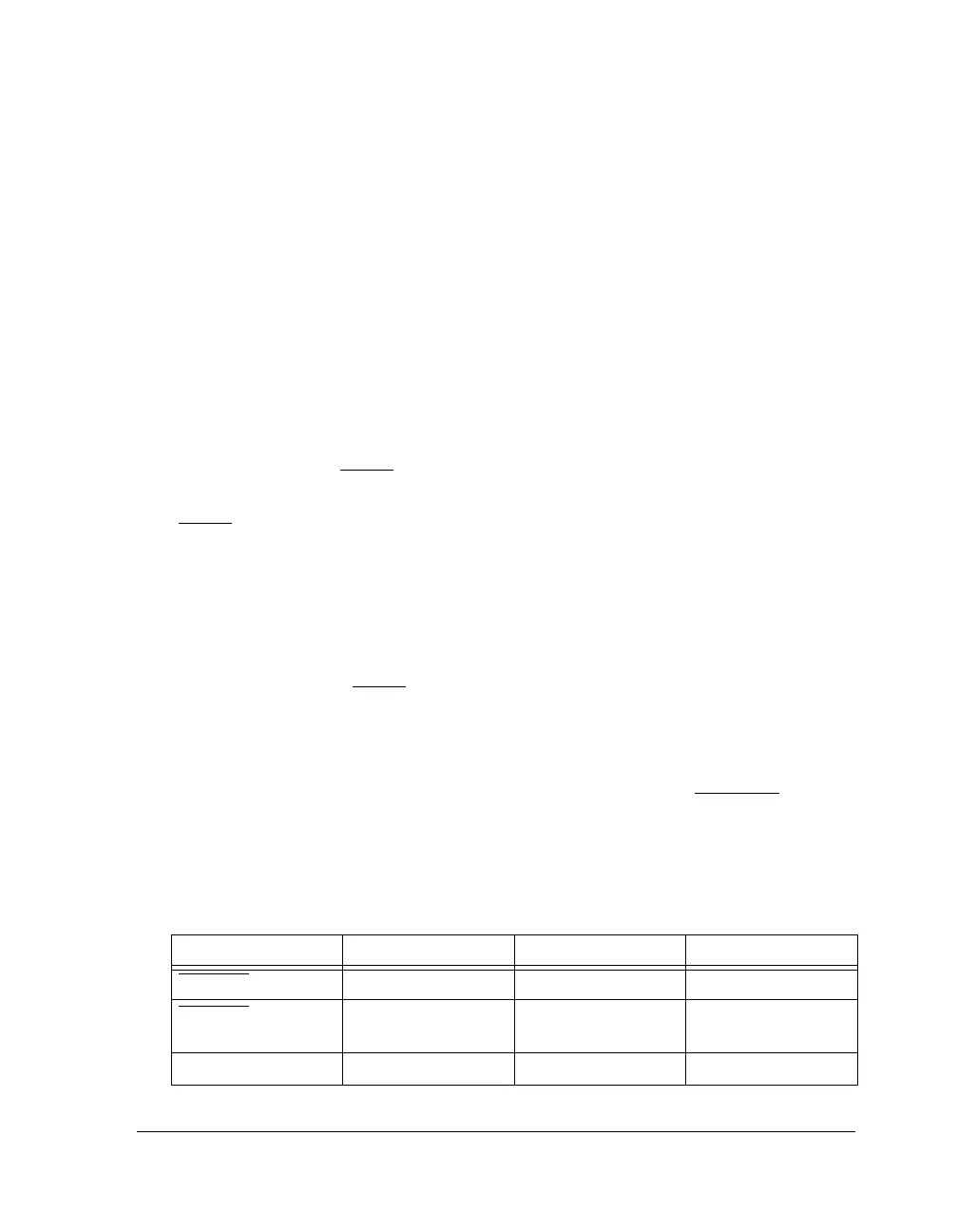

Table 23-1. Reset Function Overview

Reset Function Hardware Reset Software Reset Running Reset

RESETOUT Pin Output Output Input

RESETOUT Pulse 4096 CLKIN cycles

asserted

2 PCLK cycles asserted N/A

PLL Yes No No

Loading...

Loading...