ADSP-214xx SHARC Processor Hardware Reference 3-117

External Port

AMI Data Throughput

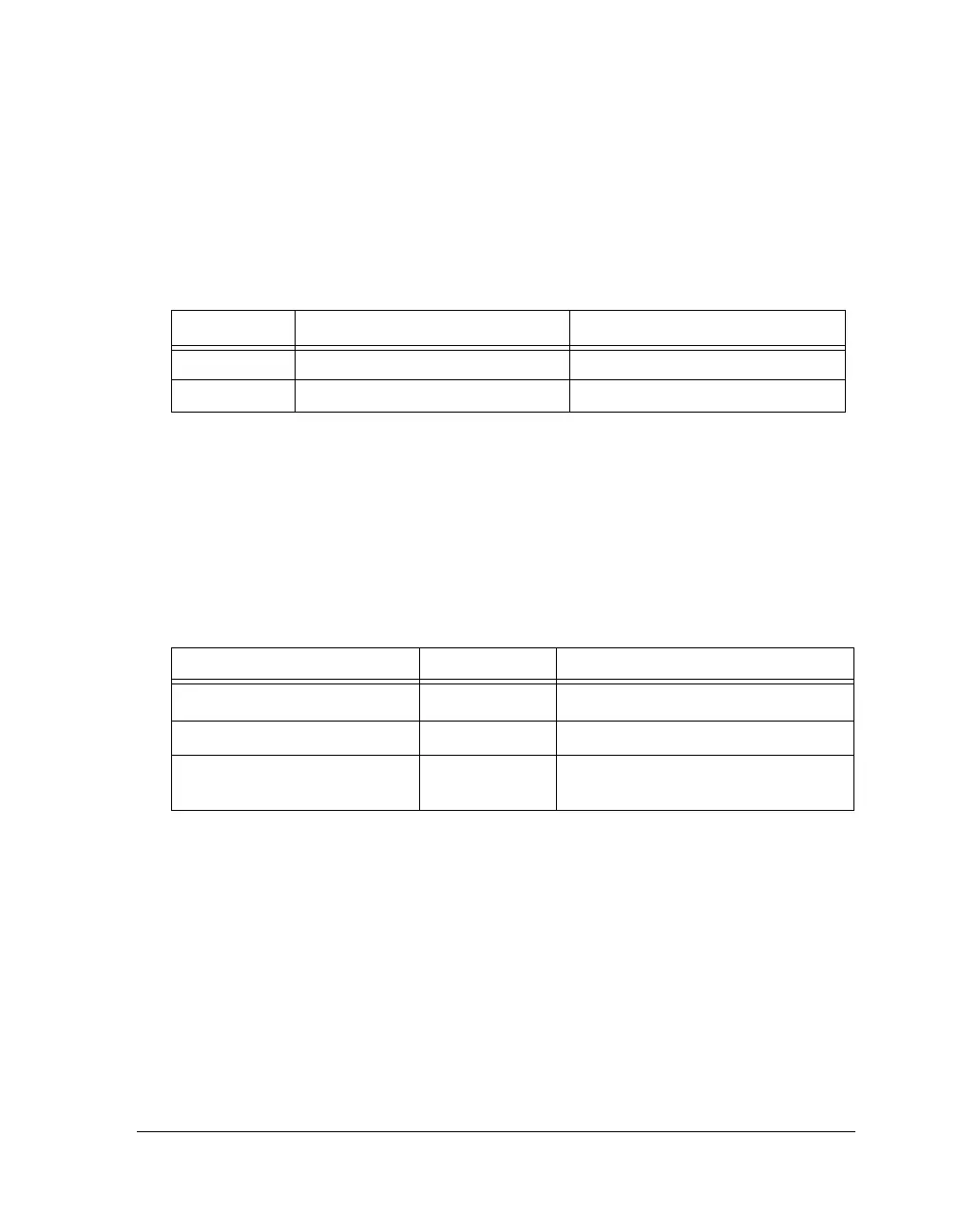

The AMI data throughput is shown in Table 3-29.

SDRAM Throughput

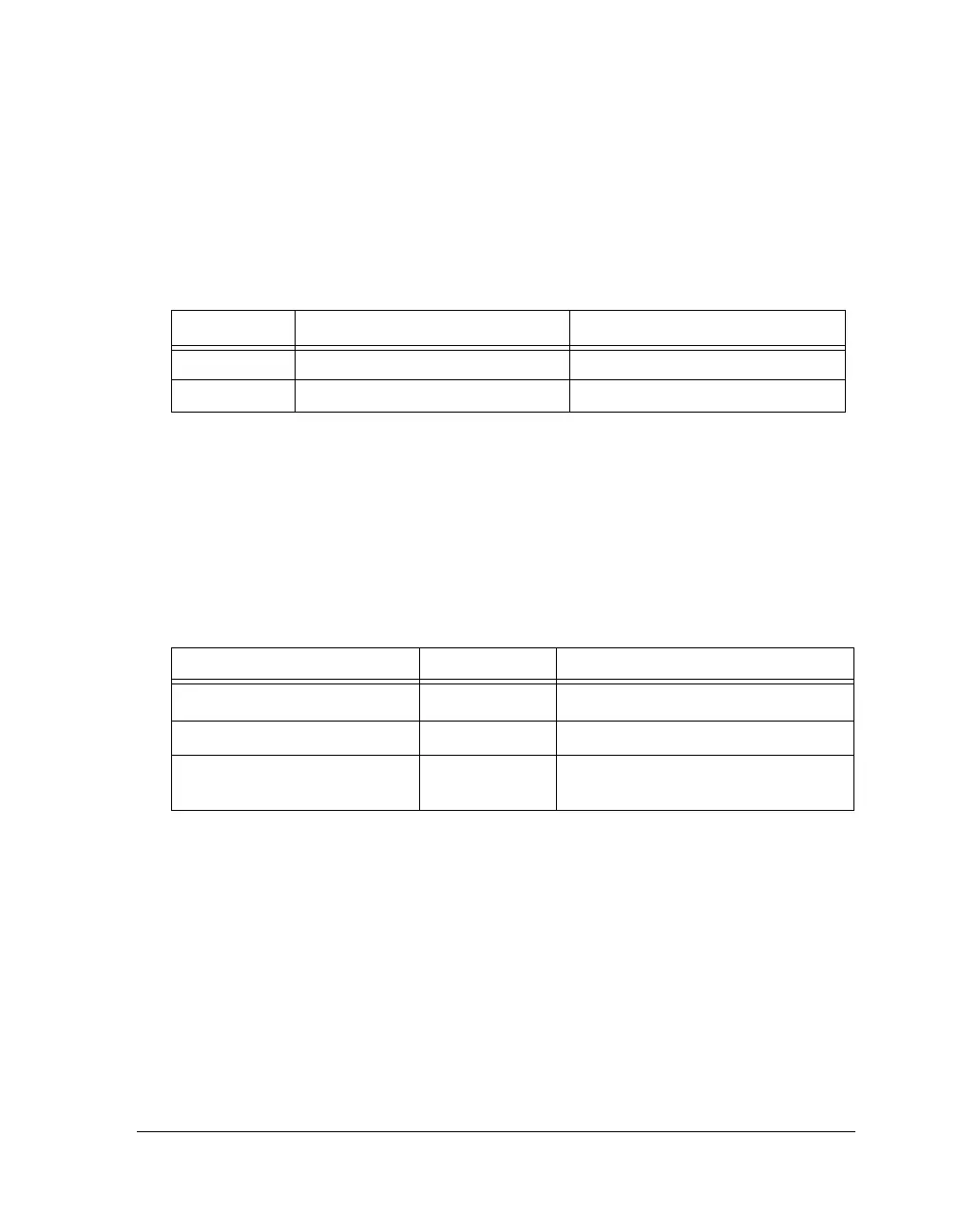

Table 3-30 provides information needed to configure the SDRAM inter-

face for the desired throughput.

Throughput Conditional Instructions

A conditional read/write may take 1

PCLK cycle (access made and access

aborted, respectively). For more information, see “External Memory

Access Restrictions” on page 3-132.

Table 3-29. Read/Write Throughput

Access

1

1 Throughput for minimum wait states of 2 with no idle and hold cycles.

8-Bit I/O 16-Bit I/O

Write 32-bit word per 12 cycles 32-bit word per 6 cycles

Read 32-bit word per 12 cycles 32-bit word per 6 cycles

Table 3-30. SDRAM Data Throughput

Access Page Throughput per SDCLK (16-Bit Data)

Sequential uninterrupted reads Same

One word per two cycles

1

1 Optimization enabled, first data of a sequential read takes 7 cycles for CL =2 and 8 cycles for

CL = 3, thereafter it is one word per two cycles.

Any writes Same 2 cycles

Non sequential

uninterrupted reads

Same 7 cycles

Loading...

Loading...