Peripherals Routed Through the DAI

A-178 ADSP-214xx SHARC Processor Hardware Reference

Input Data Port Control Register 2 (IDP_CTL2)

This register controls the first active edge selection for channel synchroni-

zation (and is only available on the ADSP-2147x and ADSP-2148x

processors). The register is shown in Figure A-95 and described in

Table A-92.

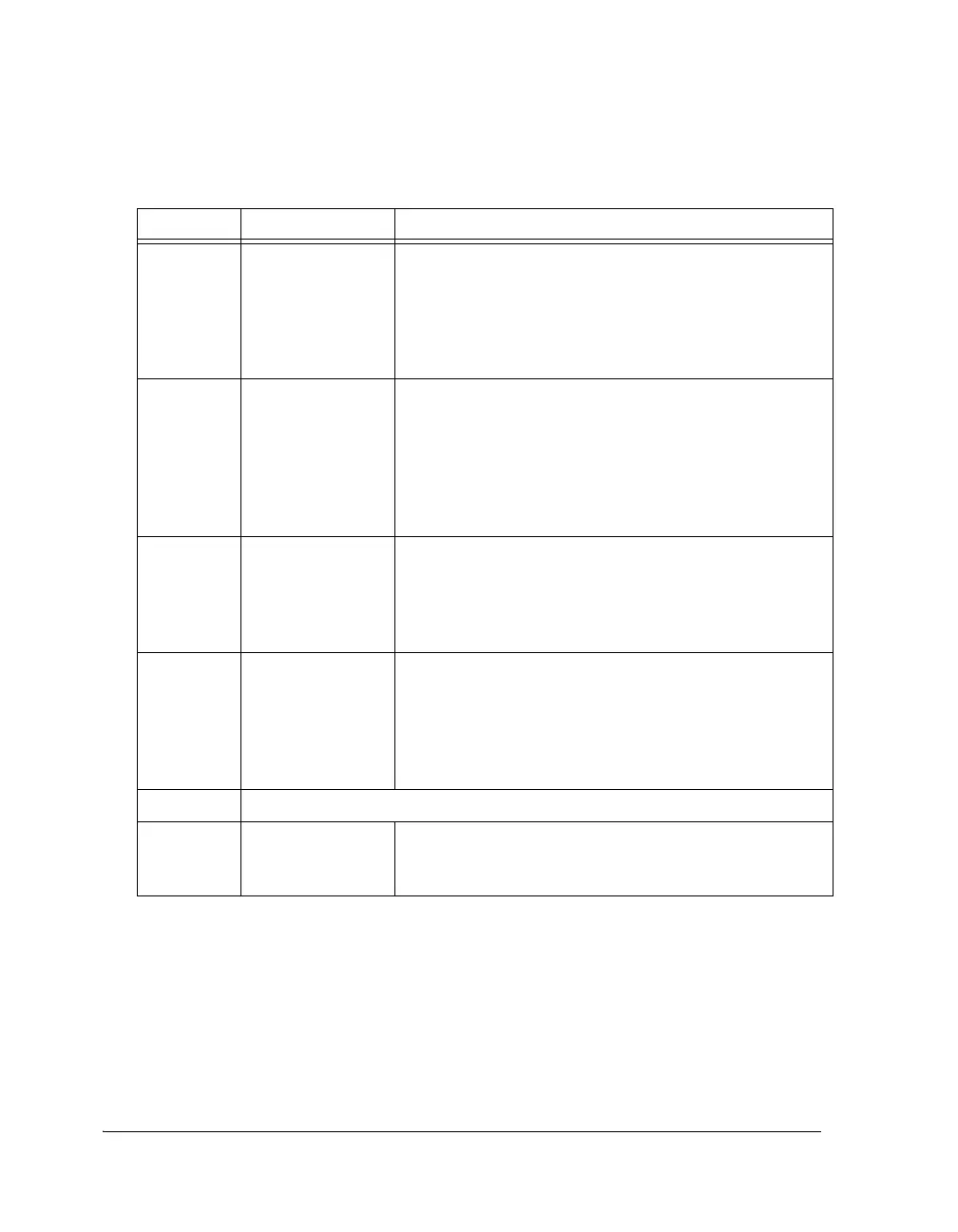

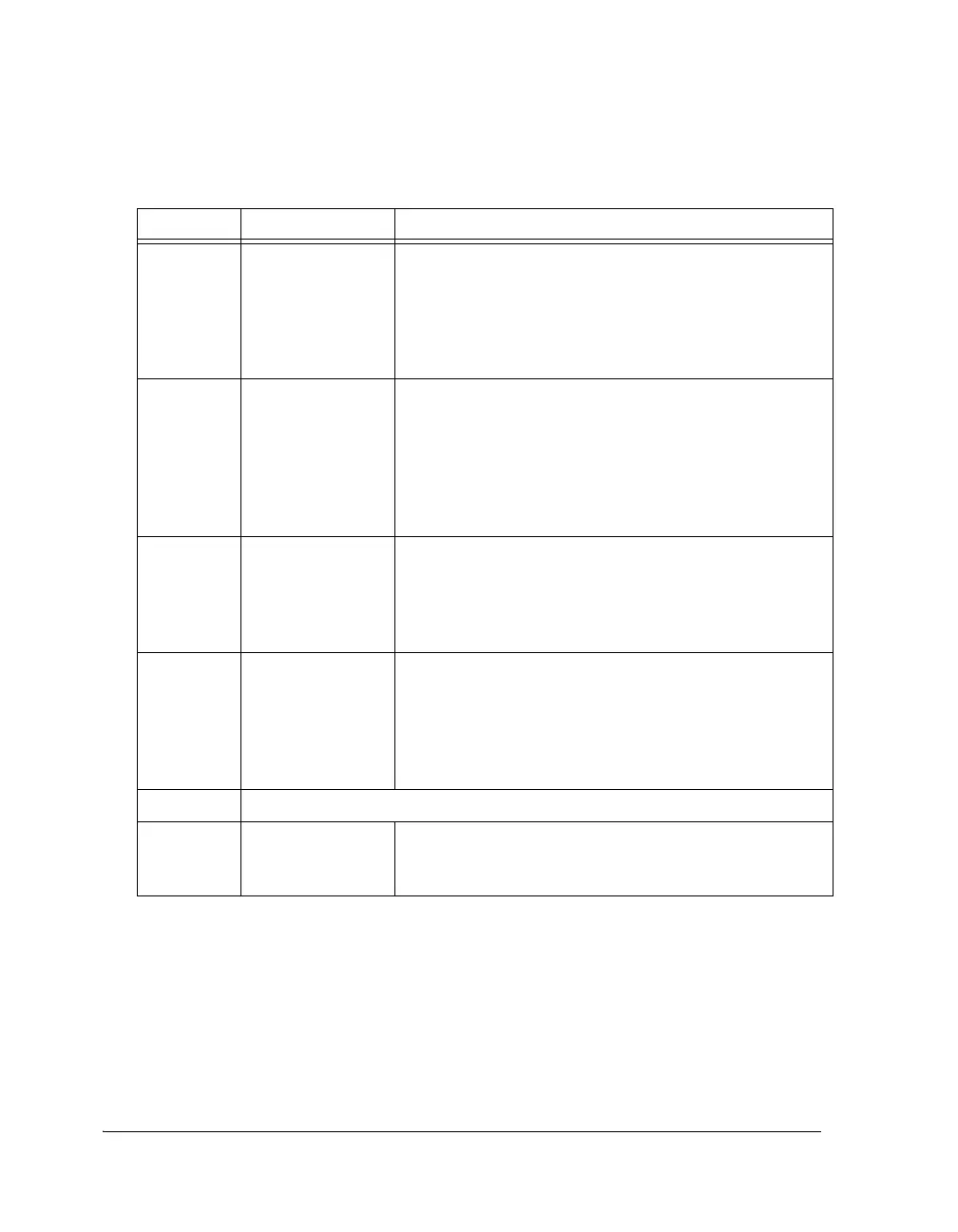

Table A-91. IDP_CTL1 Register Bit Descriptions (RW)

Bit Name Description

7–0 IDP_ENx IDP Channel x Enable. These are the enable bits for accept-

ing data from individual channels. Corresponding IDP_ENx

must be set with IDP_EN bit to get data from channel x. If

IDP_EN bit is not set then this bit has no effect.

0x00 = all channels cleared

0xFF = all channels enabled (default)

15–8 IDP_DMA_ENx IDP DMA Enable. These are the DMA enable bits for indi-

vidual channels. Corresponding IPD_DMA_ENx must be set

with IDP_DMA_EN bit for DMA transfer of data from

channel x. If the global DMA_EN bit is not set then this bit

has no effect.

0x00 = all channels cleared

0xFF = all channels enabled (default)

23–16 IDP_PINGx IDP Ping-Pong DMA Channel x Enable. These are the

Ping-Pong DMA enable bits for individual channels. Corre-

sponding IDP_PINGx must be set to start ping-pong DMA

from channel x. This bit requires the IDP_DMA_ENx bit

and IDP_DMA_EN bit are set.

24 IDP_INTEN Independent Channel Synchronization Enable. This is the

enable bit for independent channel synchronization. If this

bit is set, the IDP channels will start shifting in data from the

first active edge of the LRCLK based on the setting of FAEx.

If this bit is cleared (reset value), then the ADSP-214xx

behaves like previous SHARC processors.

30–25 Reserved

31 (WOC) IDP_FFCLR Clear IDP FIFO. Setting this bit to 1 clears the IDP FIFO

and the IDP_FIFOSZ bits. Note that when the IDP_EN bit

transitions from 1 to 0, all data in the IDP FIFO are flushed.

Loading...

Loading...