ADSP-214xx SHARC Processor Hardware Reference 10-27

Serial Ports

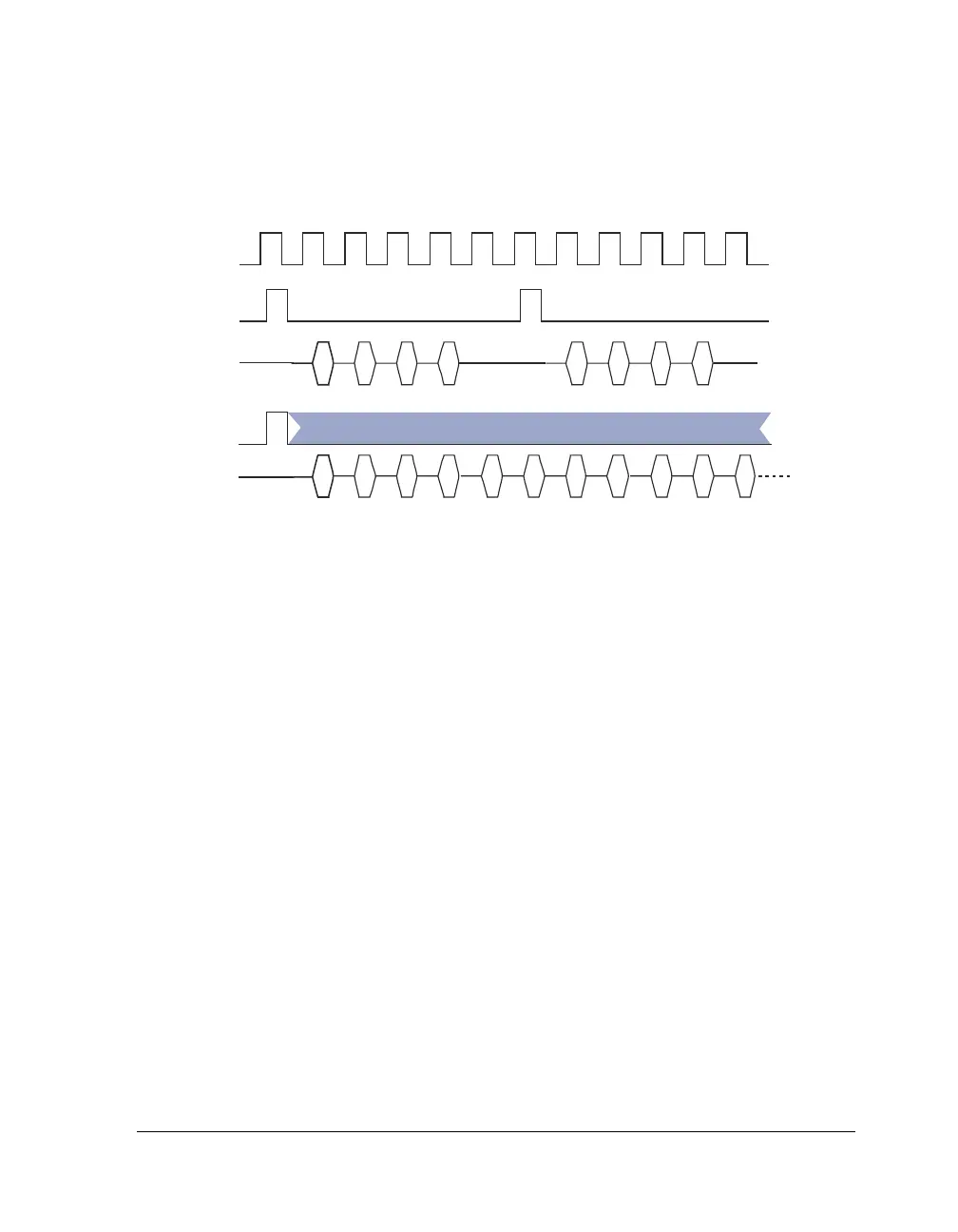

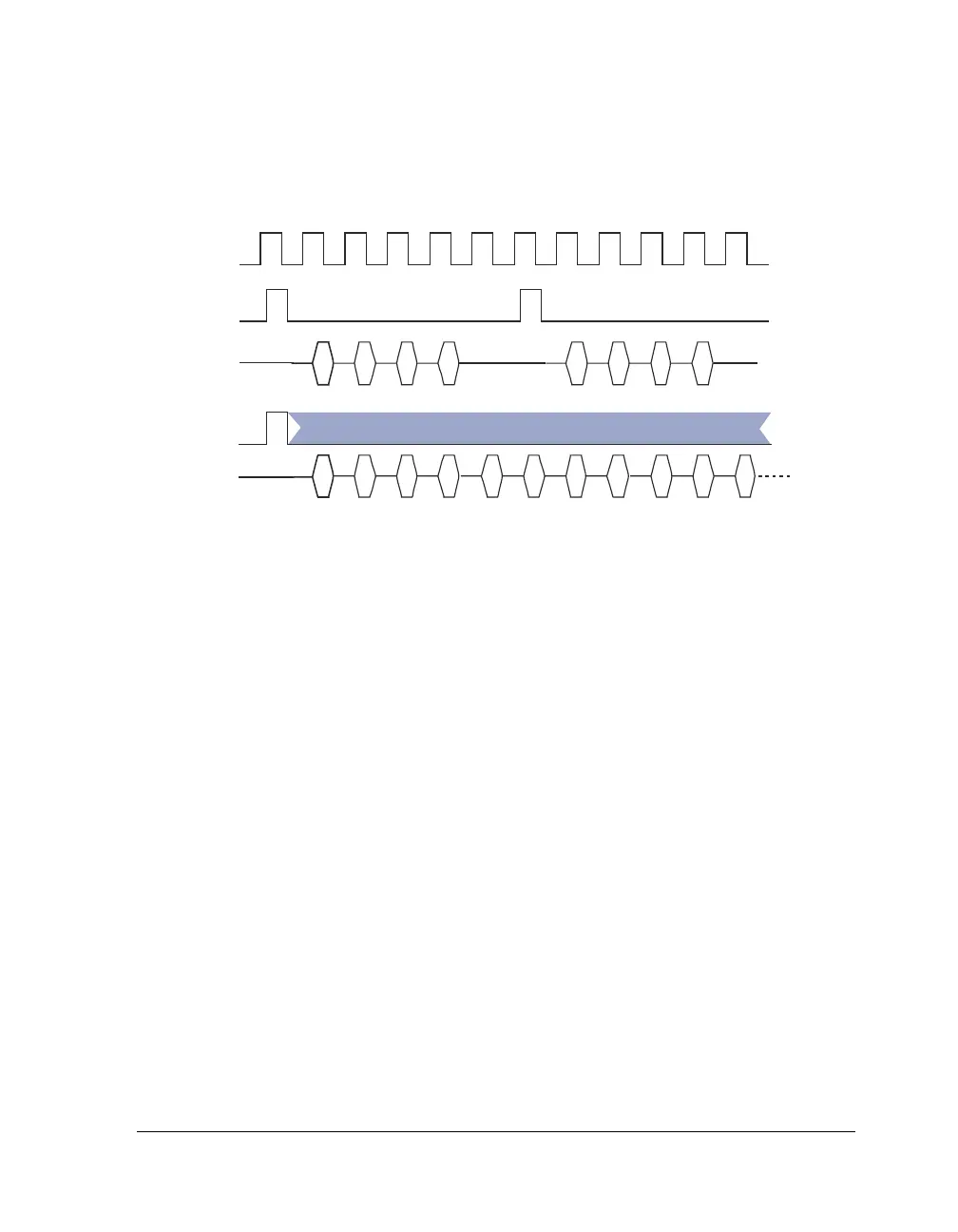

Figure 10-4 illustrates framed serial transfers.

Early Versus Late Frame Syncs

Frame sync signals can be early or late. Frame sync signals can occur dur-

ing the first bit of each data word or during the serial clock cycle

immediately preceding the first bit. The

LAFS bit of the SPCTLx control

register configures this option.

When LAFS is cleared (=0), early frame syncs are configured. This is the

normal mode of operation. In this mode, the first bit of the transmit data

word is available (and the first bit of the receive data word is latched) in

the serial clock cycle after the frame sync is asserted. The frame sync is not

checked again until the entire word has been transmitted (or received). In

multichannel operation, this is the case when the frame delay is one.

If data transmission is continuous in early framing mode (for example, the

last bit of each word is immediately followed by the first bit of the next

word), the frame sync signal occurs during the last bit of each word. Inter-

nally-generated frame syncs are asserted for one clock cycle in early

framing mode.

Figure 10-4. Framed Versus Unframed Data

B

3

B

2

B

1

B

0

B

3

B

2

B

1

B

0

B

3

B

2

B

1

B

0

B

3

B

2

B

1

B

0

B

3

B

2

B

1

SPORTX_CLK

FRAMED

DATA

UNFRAMED

DATA

Loading...

Loading...