IIR Accelerator

6-62 ADSP-214xx SHARC Processor Hardware Reference

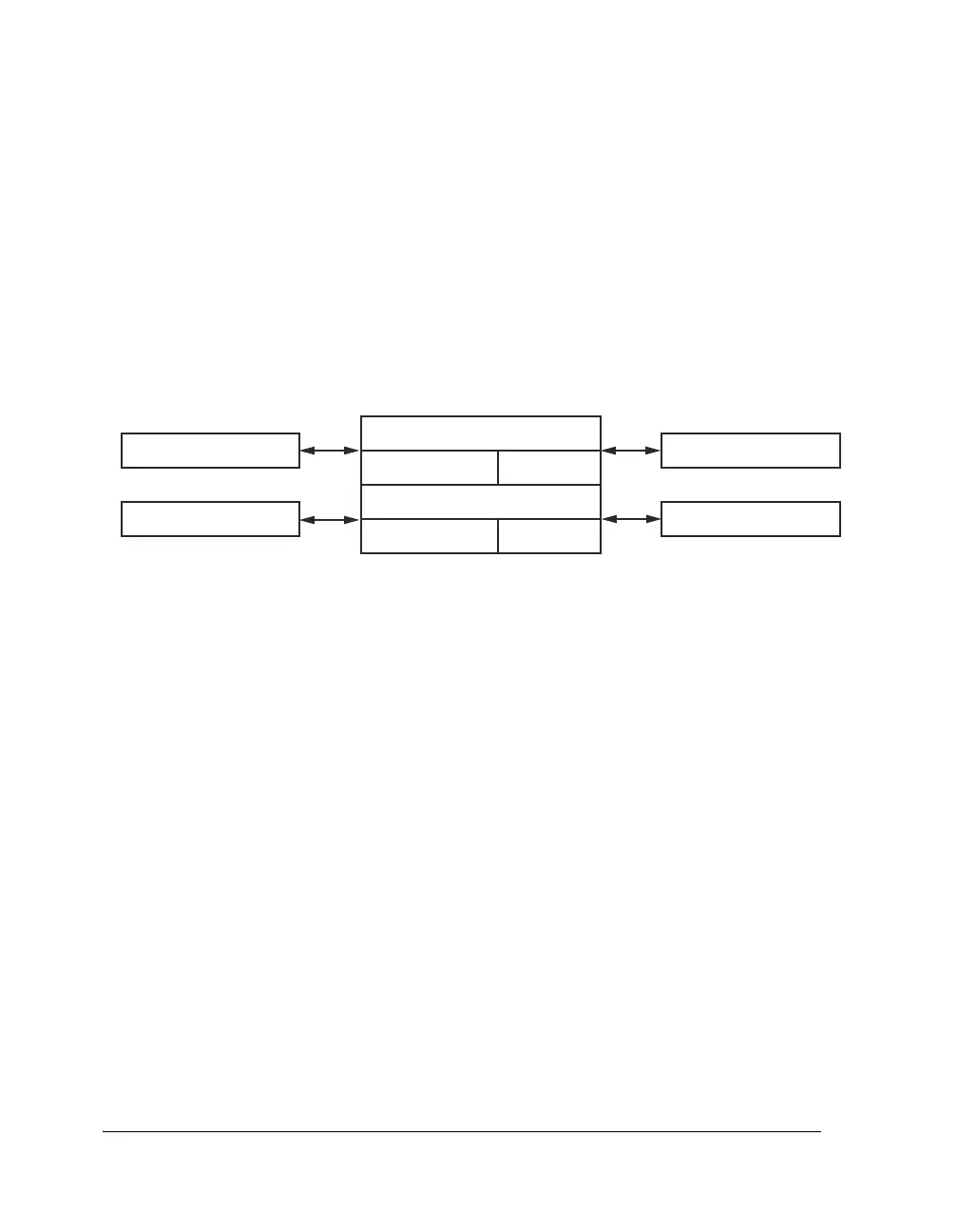

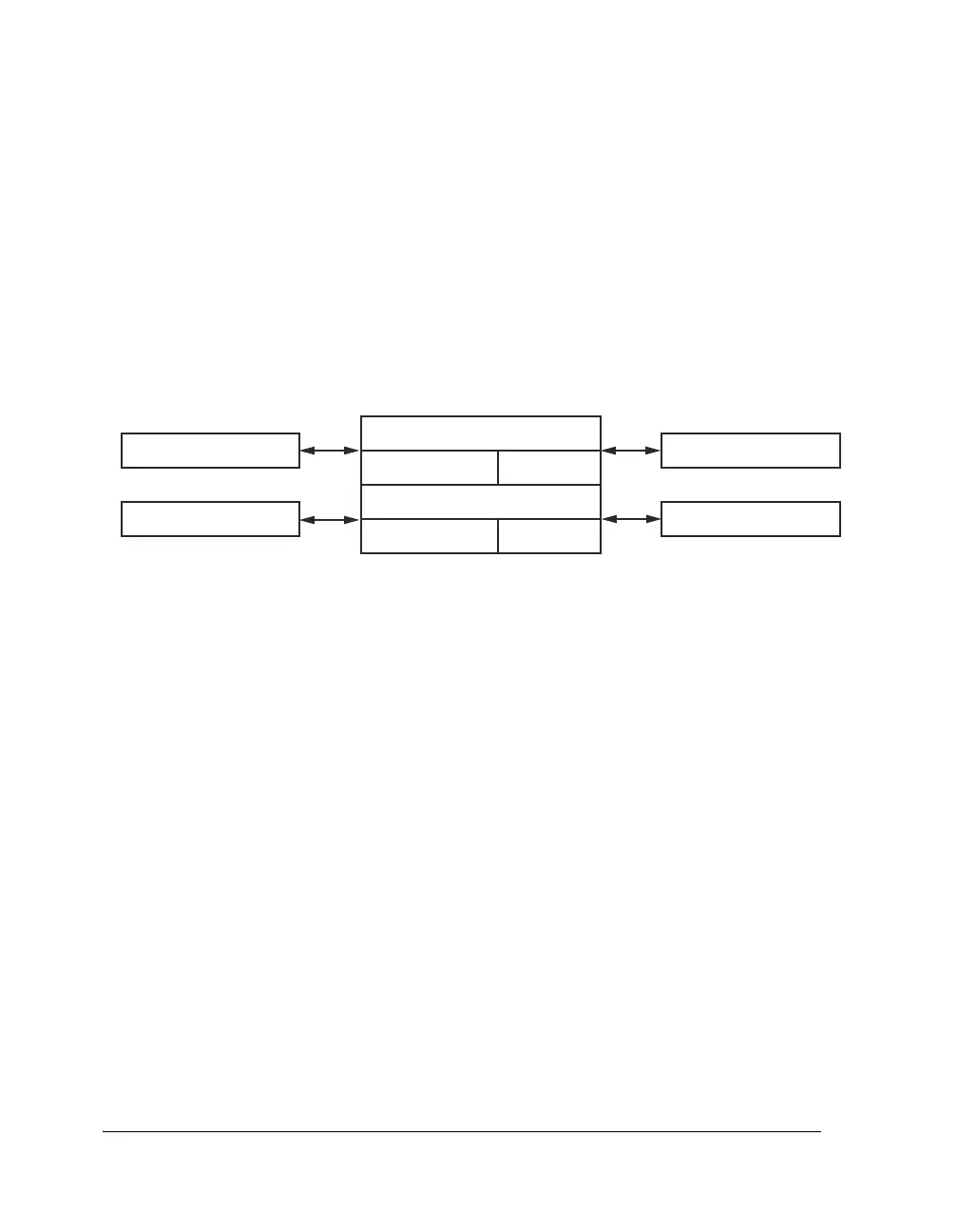

first 32-bit word provides the lower 32 bits and the 8 LSBs of the second

32-bit word provides rest of the upper 8 bits of the a complete 40-bit

word. Figure 6-12 shows the 32-40 bit packing used by accelerator.

Overheads might be required to pack the input 40-bit data into the

format acceptable by the IIR accelerator and for unpacking the

output of accelerator to the format acceptable by the rest of the

application.

Data Transfers

The IIR filter works exclusively through DMA.

DMA Access

The IIR accelerator has two DMA channels (accelerator input and output)

to connect to the internal memory. The DMA controller fetches the data

and coefficients from memory and stores the result.

Chain Pointer DMA

The DMA controller supports circular buffer chain pointer DMA. One

transfer control block (TCB) needs to be configured for each channel. The

TCB contains:

Figure 6-12. 32- to 40-Bit Packing

DATA1 [ 31—0]

DATA2 [31—0]

DATA2 [39—0]

DATA1 [39—0]

X

X+1

X+2

X+3

IOD0 DMA BUS (32-BIT)

IIR ACCELERATOR

(40-BIT) MEMORY

DATA1 [39—31]

DATA2 [39—31]

DATA2 [39—0]

DATA1 [39—0]

3 COLUMN INTERNAL

MEMORY (40-BIT)

Loading...

Loading...