Peripheral Registers

A-90 ADSP-214xx SHARC Processor Hardware Reference

IIR Channel Control Register (IIRCTL2)

The

IIRCTL2 register, shown in Figure A-41 and described in Table A-53,

is used to configure the channel specific parameters. These include num-

ber of biquads and window size.

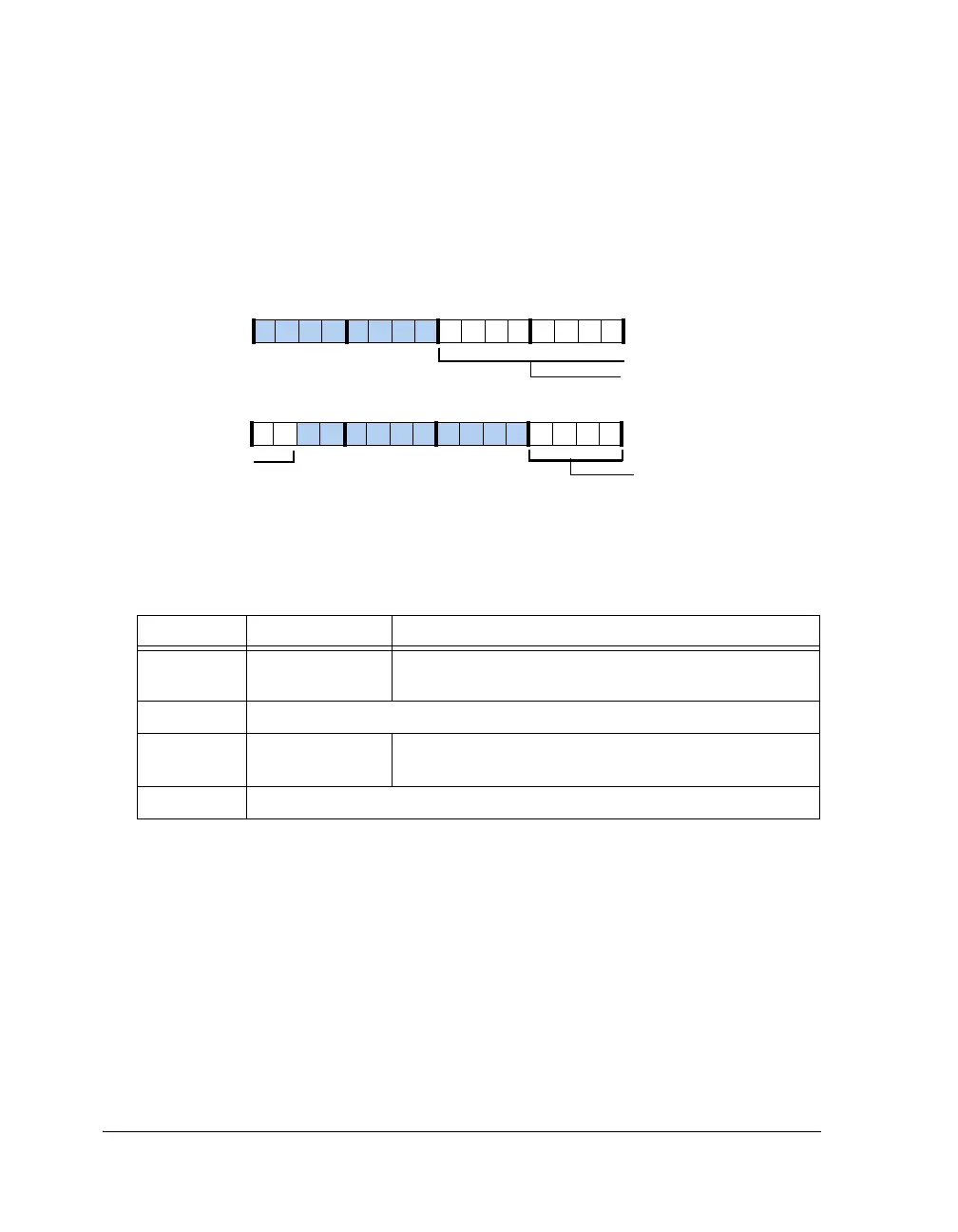

Figure A-41. IIRCTL2 Register

Table A-53. IIRCTL2 Register Bit Descriptions (RW)

Bits Name Description

3–0 IIR_NBIQUADS Number of Biquads. Programmable between 0–11. Number

of Biquads = BIQUADS + 1

13–4 Reserved

23–14 IIR_WINDOW Window Size Parameter. Programmable between 0–1023.

Window Size = WINDOW+ 1

31–24 Reserved

IIR_NBIQUADS (3–0)

IIR_WINDOW (23–14)

Window Size

Number of Biquads

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

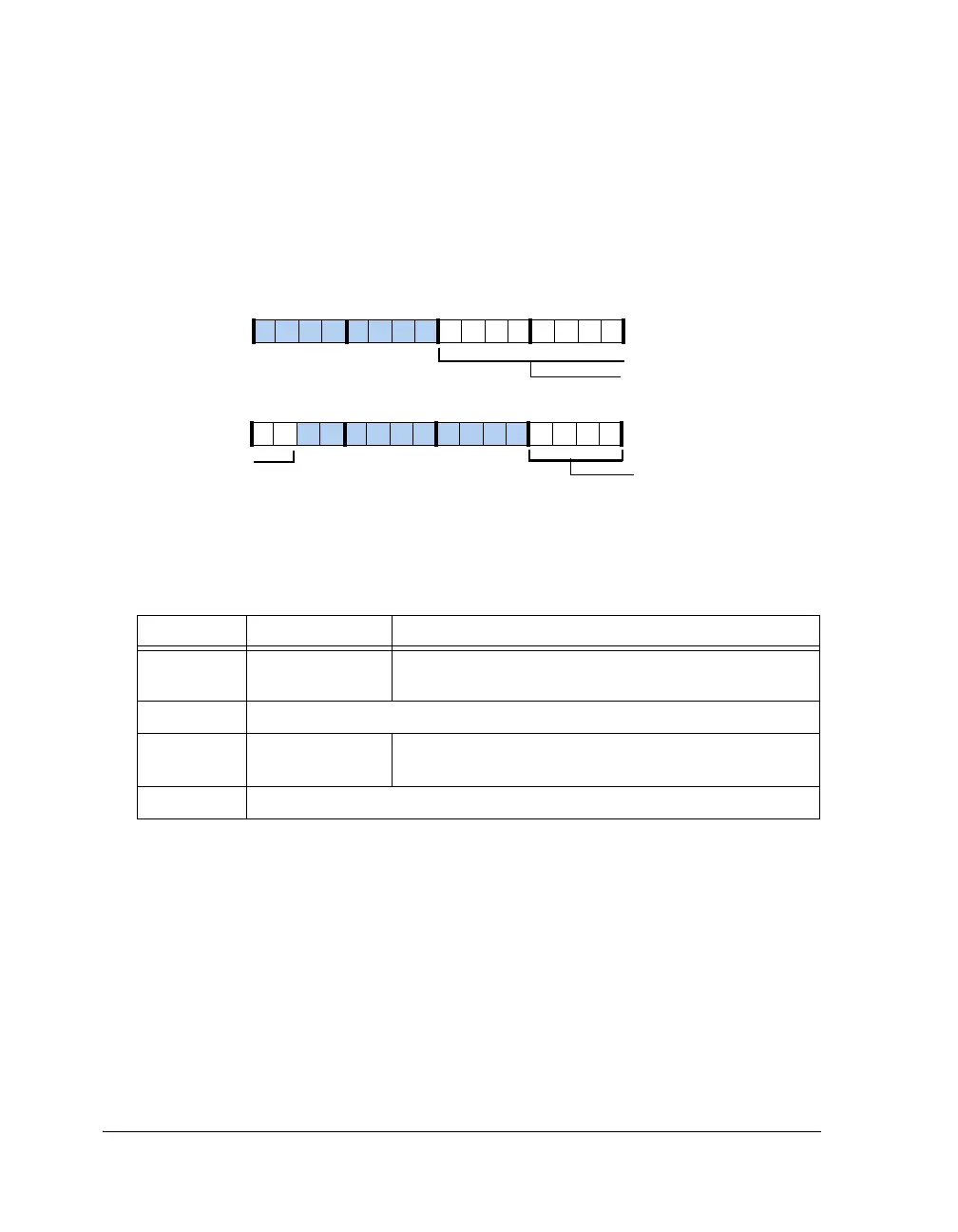

IIR_WINDOW (23–14)

Window Size

Loading...

Loading...