ADSP-214xx SHARC Processor Hardware Reference A-89

Registers Reference

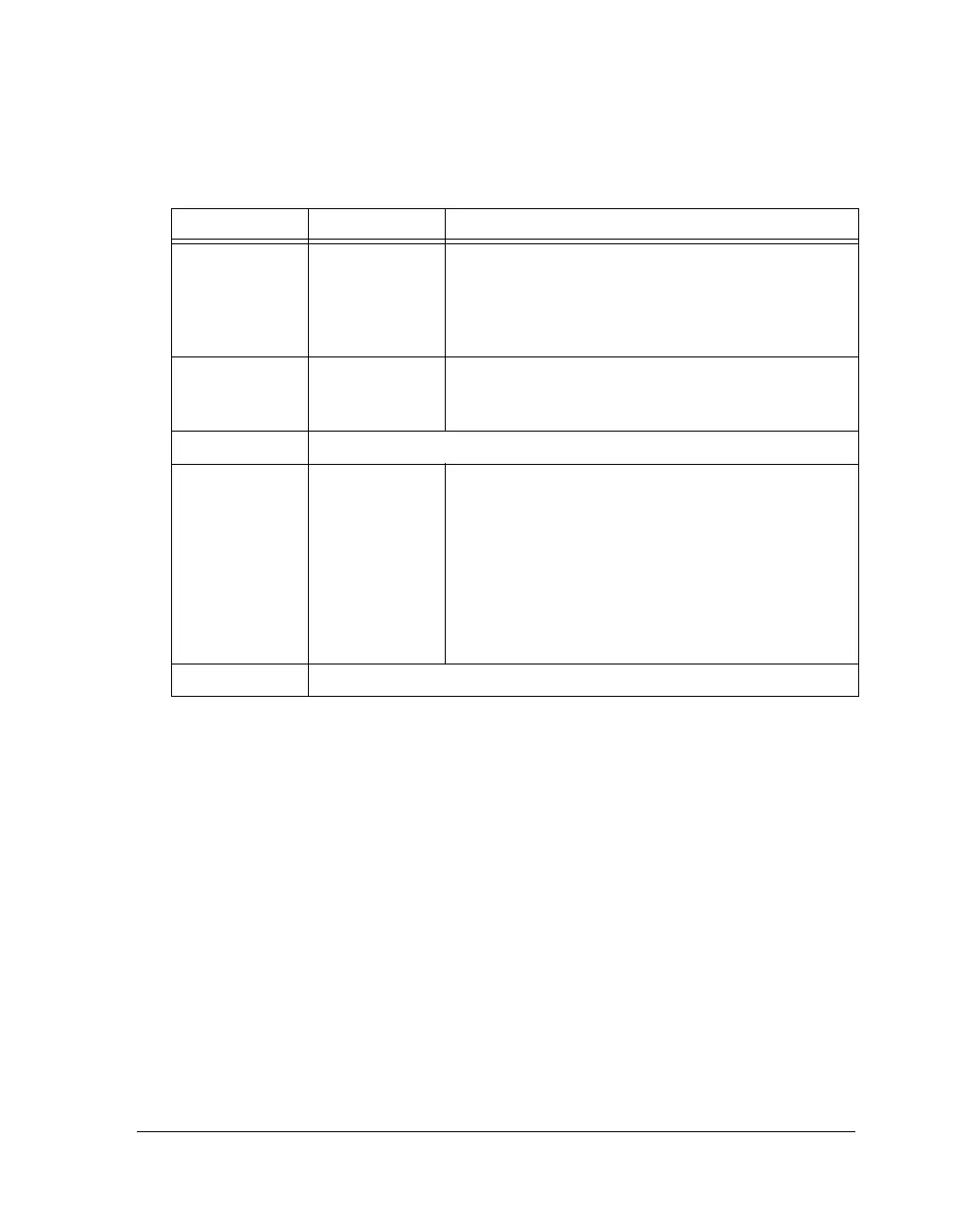

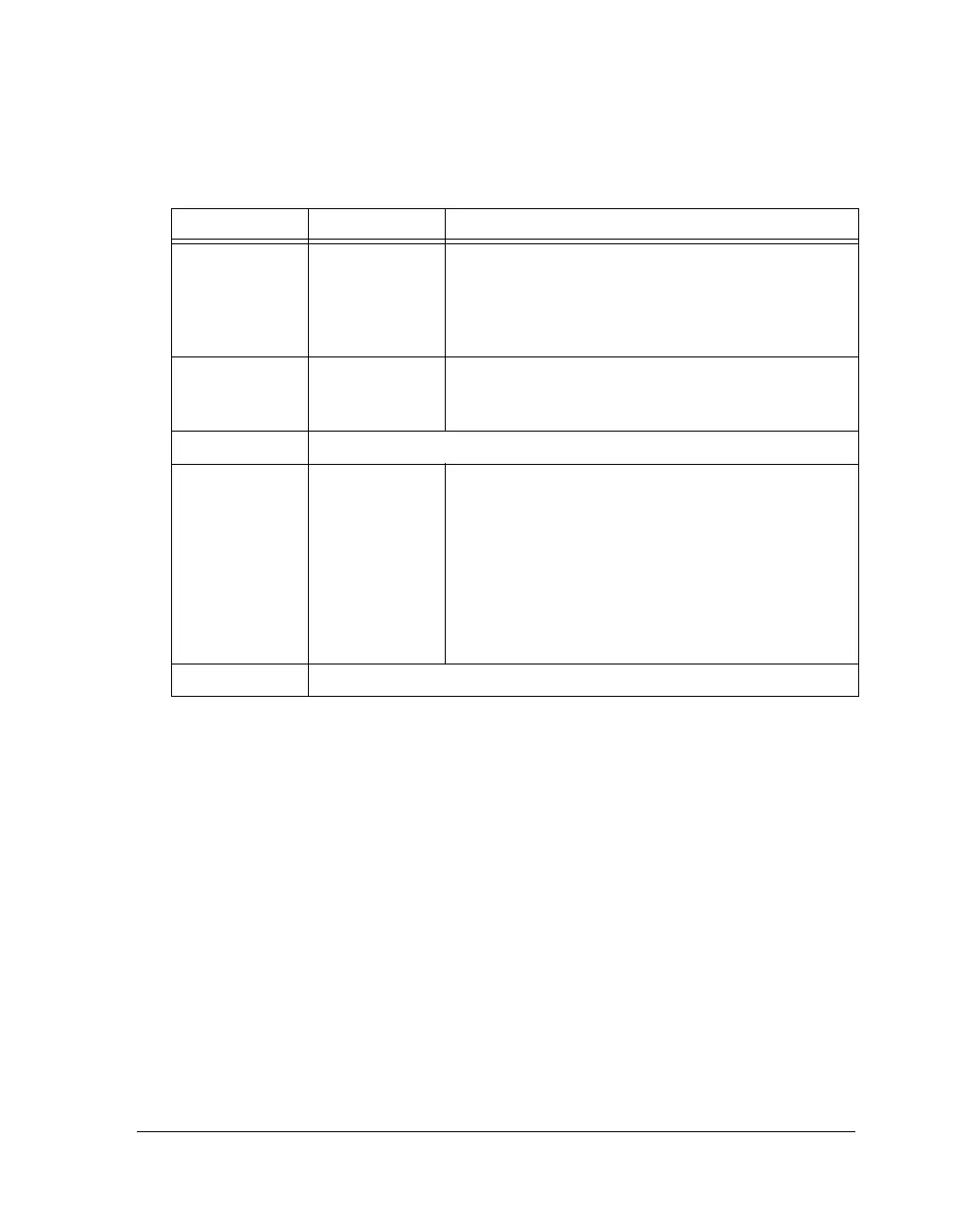

11 IIR_CCINTR Channel Complete Interrupt.

0 = Interrupt is generated only when all channels are done

(default)

1 = Interrupt is generated after each channels is done

(default)

12 IIR_FORTYBIT 40-Bit Floating-Point Format Select.

0 = 32-bit IEEE floating-point

1 = 40-bit IEEE floating-point

13 Reserved

16–14 IIR_RND Rounding Mode Select for Floating-Point Mode.

000 = IEEE round to nearest (even)

001 = IEEE round to zero

010 = IEEE round to +ve infinity

011 = IEEE round to -ve infinity

100 = Round to nearest Up

101 = Round away from zero

110 = Reserved

111 = Reserved

31–17 Reserved

Table A-52. IIRCTL1 Register Bit Descriptions (RW) (Cont’d)

Bits Name Description

Loading...

Loading...