ADSP-214xx SHARC Processor Hardware Reference A-247

Registers Reference

Interrupt Identification Registers (UART0IIR,

UART0IIRSH)

For legacy reasons, the UART interrupt identification register (UART0IIR,

shown in Figure A-139) still reflect the UART interrupt status. Legacy

operation may require bundling all UART interrupt sources to a single

interrupt channel and servicing them all by the same software routine.

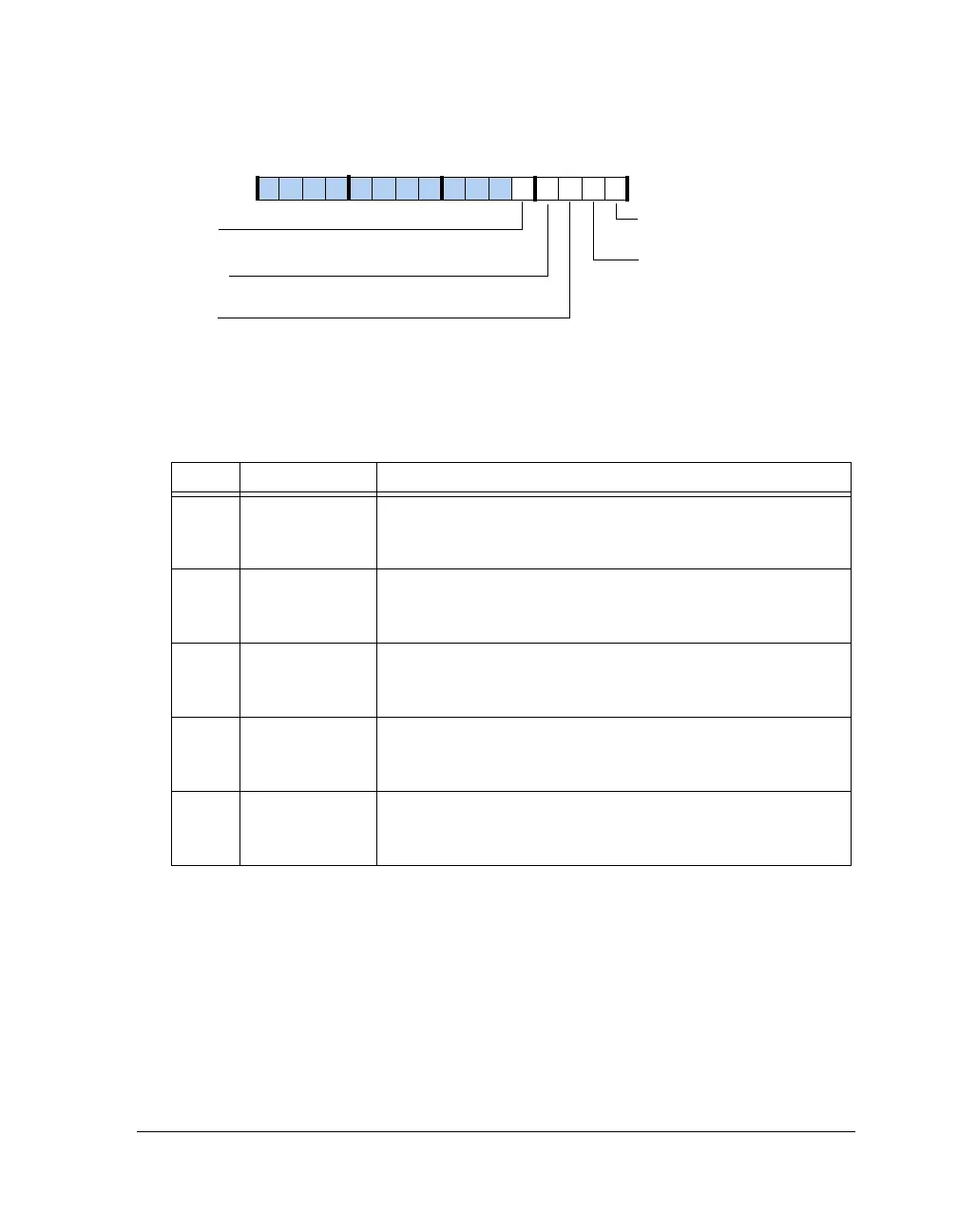

Figure A-138. UART0IER Register

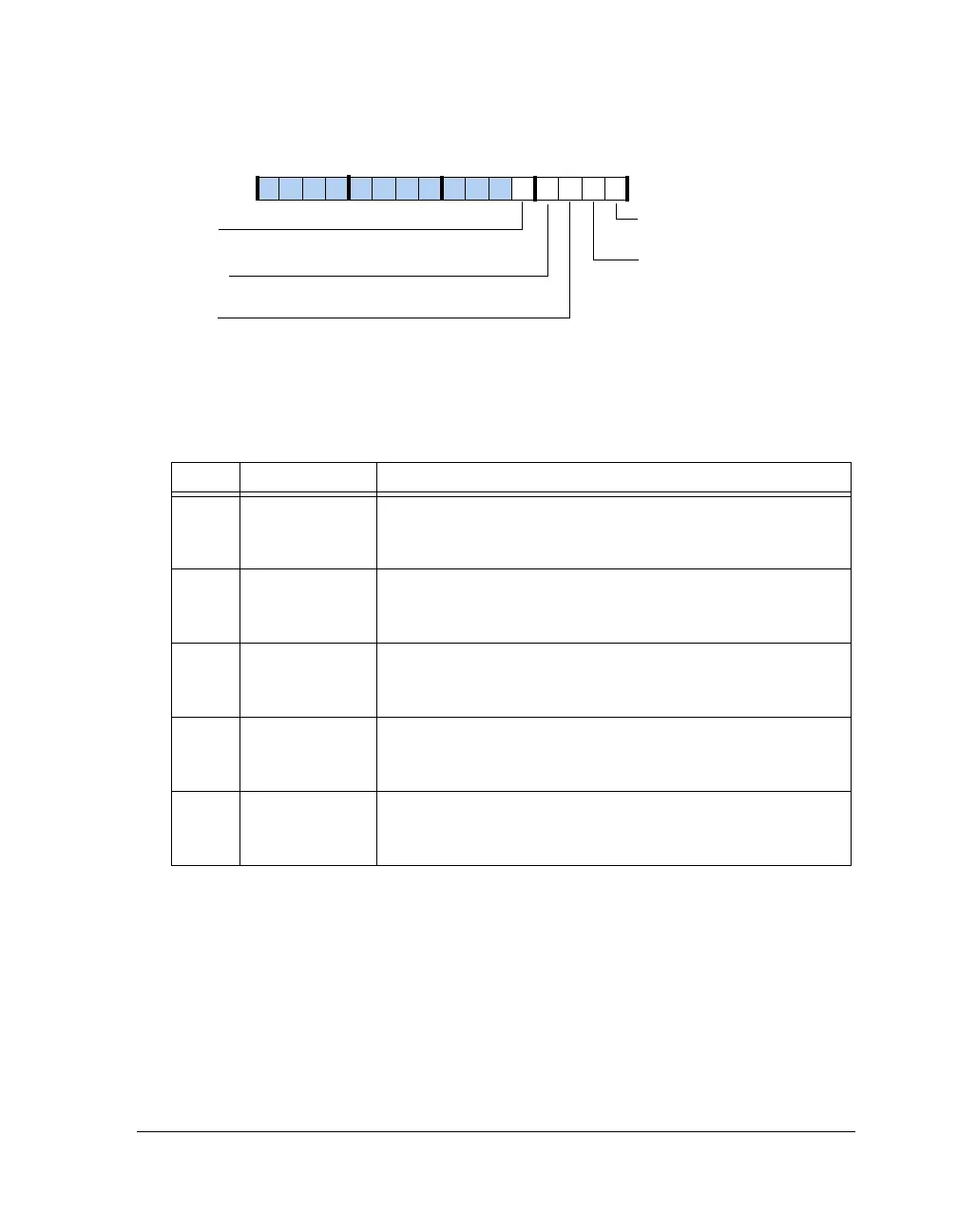

Table A-129. UART0IER Register Bit Descriptions (RW)

Bit Name Description

0 UARTRBFIE Enable Receive Buffer Full Interrupt.

0 = No interrupt

1 = Generate RX interrupt if DR bit in UART_LSR is set

1UARTTBEIE Enable Transmit Buffer Empty Interrupt.

0 = No interrupt

1 = Generate TX interrupt if THRE bit in UART_LSR is set

2UARTLSIEEnable RX Status Interrupt.

0 = No interrupt

1 = Generate line status interrupt if any of UART_LSR[4–1] is set

3UARTTXFIEEnable Transmit Complete Interrupt.

0 = No interrupt

1 = Generate TX interrupt if TEMT bit in UART_LSR is set

4UARTADIEEnable Address Detect Interrupt in 9-Bit Mode.

0 = No interrupt

1 = Generate RX interrupt when address is detected in 9-bit mode

UARTRBFIE

UARTTBEIE

Enable Receive Buffer Full Interrupt

Enable Transmit Buffer Empty

Interrupt

UARTLSIE

Enable RX Status Interrupt

UARTTXFIE

Enable Transmit Complete Interrupt

UARTADIE

Enable Address Detect Interrupt in 9-Bit Mode

09 837564 2114 12 11 101315

Loading...

Loading...