Data Transfer

11-16 ADSP-214xx SHARC Processor Hardware Reference

The three LSBs of FIFO data are the encoded channel number. These are

transferred “as is” for this mode. These bits can be used by software to

decode the source of data.

The maximum data transfer width to internal memory is 32-bits, as

in the case of PDAP data or I

2

S and left-justified modes in single

channel mode using 32 bits of data. Therefore, PDAP or I

2

S and

left-justified 32-bit modes cannot be used with other channels in

the core/interrupt driven mode since no channel information is

available in the data stream.

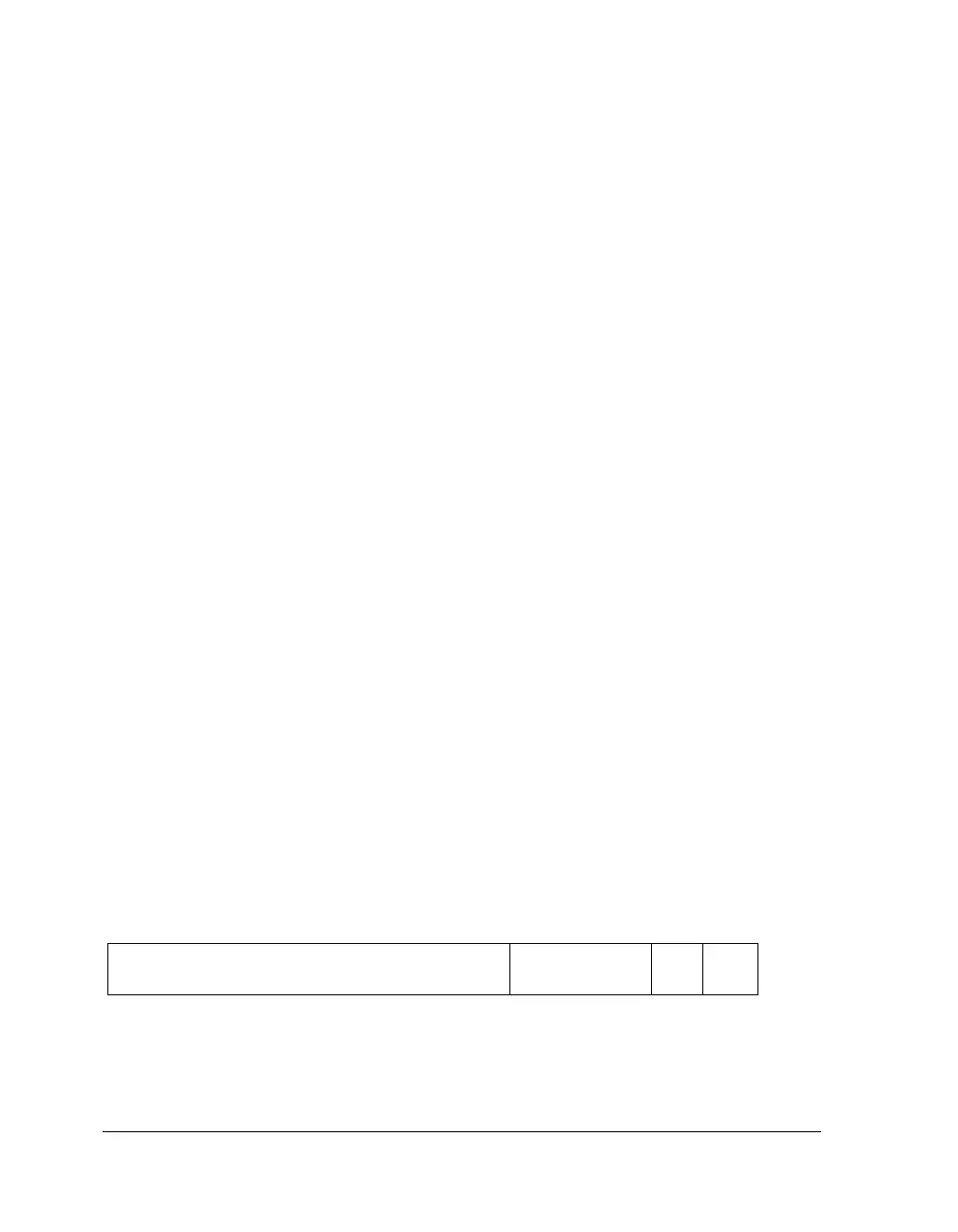

SIP Data Buffer Format

An audio signal that is normally 24 bits wide is contained within the

32-bit word. Four bits are available for status and formatting data (com-

pliant with the IEC 90958, S/PDIF, and AES3 standards). An additional

bit identifies the left-right one-half of the frame. If the data is not in IEC

standard format, the serial data can be any data word up to 28 bits wide.

Unlike DMA, the core requires a status information about which channel

triggered the interrupt. It does this by reading the data buffer. The

remaining three bits are used to encode one of the eight channels being

passed through the FIFO to the core. The FIFO output may feed eight

DMA channels, where the appropriate DMA channel (corresponding to

the channel number) is selected automatically.

Regardless of mode, the L/R channel status bit (Bit 3) always spec-

ifies whether the data is received in the left channel or the right

channel of the corresponding input frame, as shown in

Figure 11-6.

Figure 11-6. Principle Data Format for the SIP

31

8 7

4 3 20

AUDIO DATA

INVALID BITS

L/R

IDP

CHNL

Loading...

Loading...