ADSP-214xx SHARC Processor Hardware Reference A-115

Registers Reference

Current Count (WDTCURCNT)

The

WDTCURCNT register contains the current count value of the watchdog

timer. Reads to WDTCURCNT return the current count value. For added

safety, this register can only be updated when WDT configuration space is

unlocked by programming the command in the WDTUNLOCK register. Values

cannot be stored directly in WDTCURCNT, but are instead copied from

WDTCNT.

Enabling the watchdog timer does not automatically reload WDTCURCNT

from

WDTCNT. The WDTCURCNT register is a 32-bit unsigned system mem-

ory-mapped register that must be accessed with 32-bit reads and writes.

Trip Counter (WDTTRIP)

The WDT contains a software programmable register

WDTTRIP that sets

the number of times that the WDT can expire before the

WDTRSTO pin is

continually asserted until the next time hardware reset is applied. This reg-

ister is unaffected by WDT generated reset. This register can only be

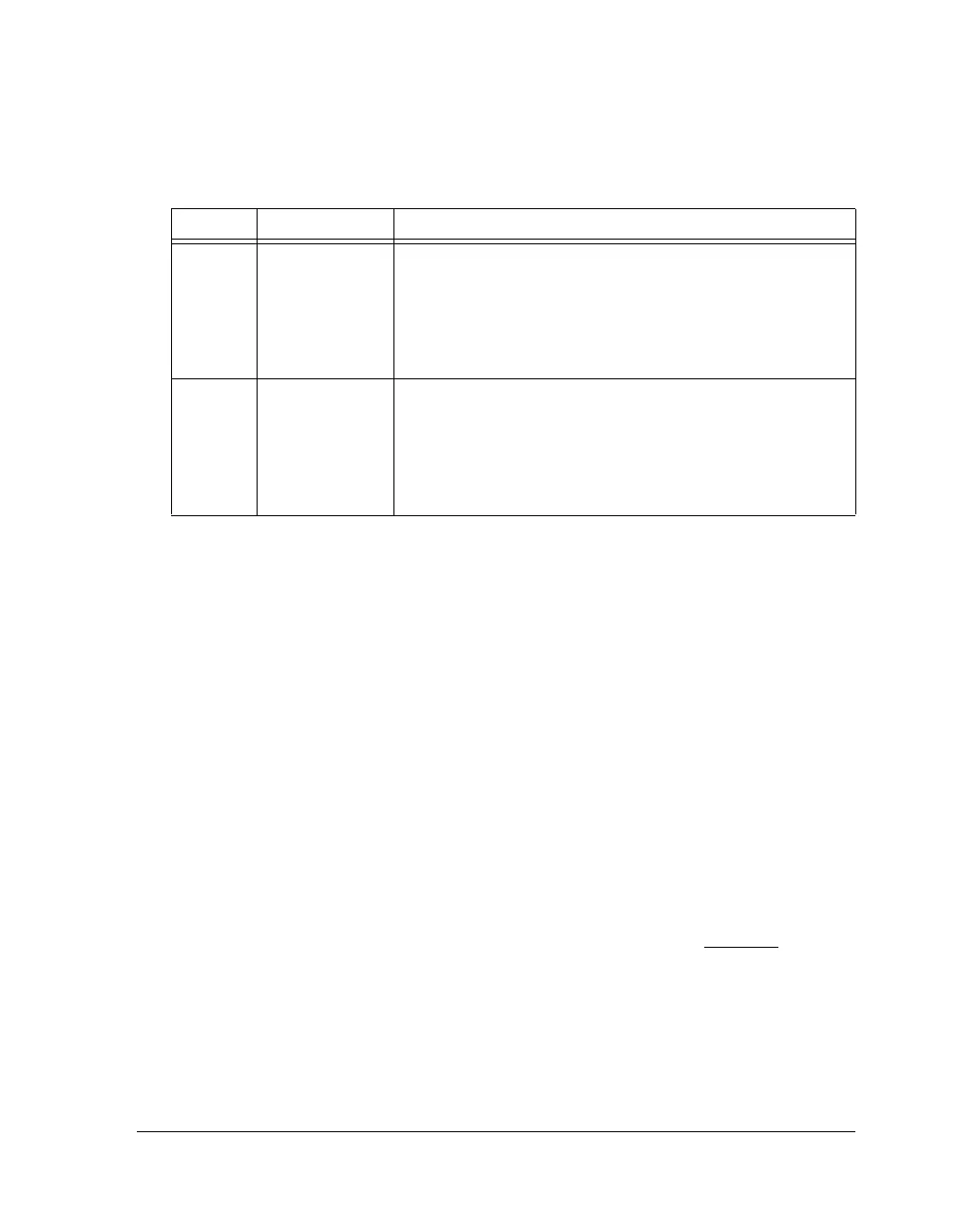

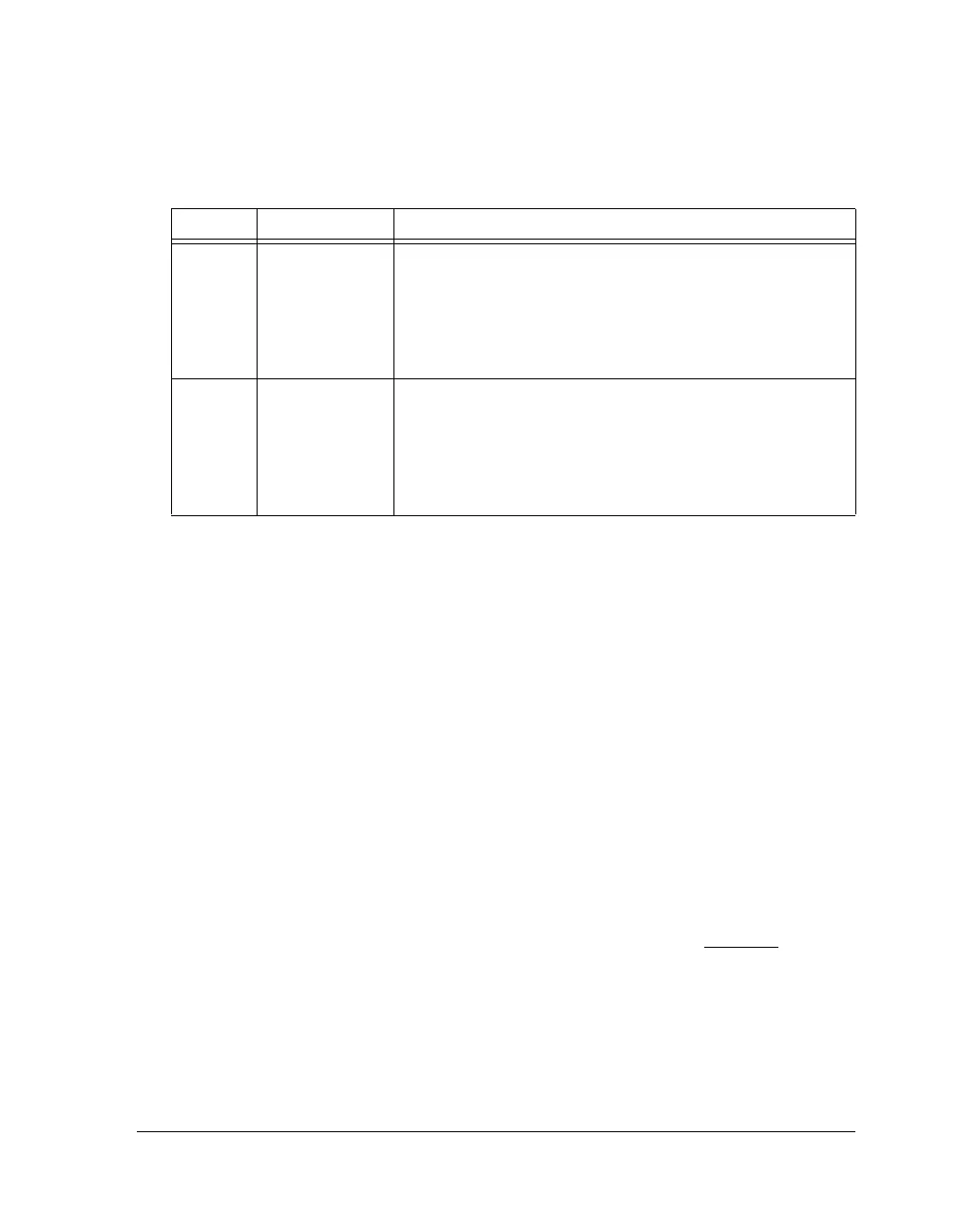

Table A-72. WDTSTATUS Register Bit Descriptions (RO)

Bit Name Description

0 (W1C) WDRO Watchdog Expired. Indicates that DSP core attempted to write

to WDT configuration space without an unlock “command”. Bit

is set when the above exception occurs. Software can determine

whether the watchdog has expired by interrogating this bit. This

is a sticky bit that is set whenever the watchdog timer count

reaches 0.

1 (W1C) WDERR Watchdog Error. Indicates that watchdog timer has expired. Bit

is set when counter expires. Attempts by the core to write to the

WDT configuration space without an unlock command, causes

the WDT to expire and this condition is captured in the watch-

dog exception field. This is a sticky bit that is set whenever the

above exception occurs.

Loading...

Loading...