ADSP-214xx SHARC Processor Hardware Reference 3-87

External Port

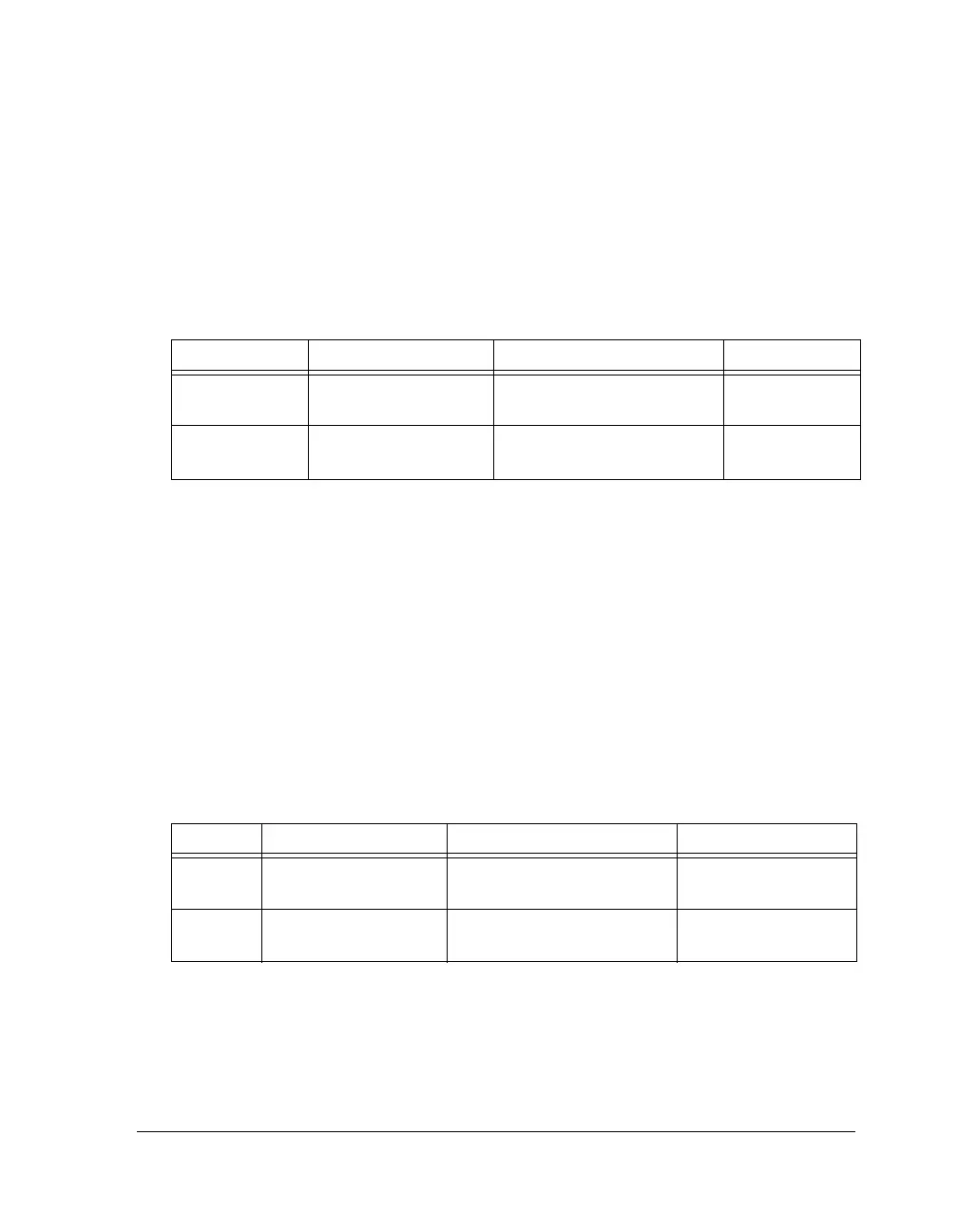

The first access does the explicit 32-bit access (which results in the physi-

cal space in 2x16-bit words) while the 2nd 32-bit access does the implicit

transfer. In total there are four read or write commands as shown in

Table 3-16.

DDR2

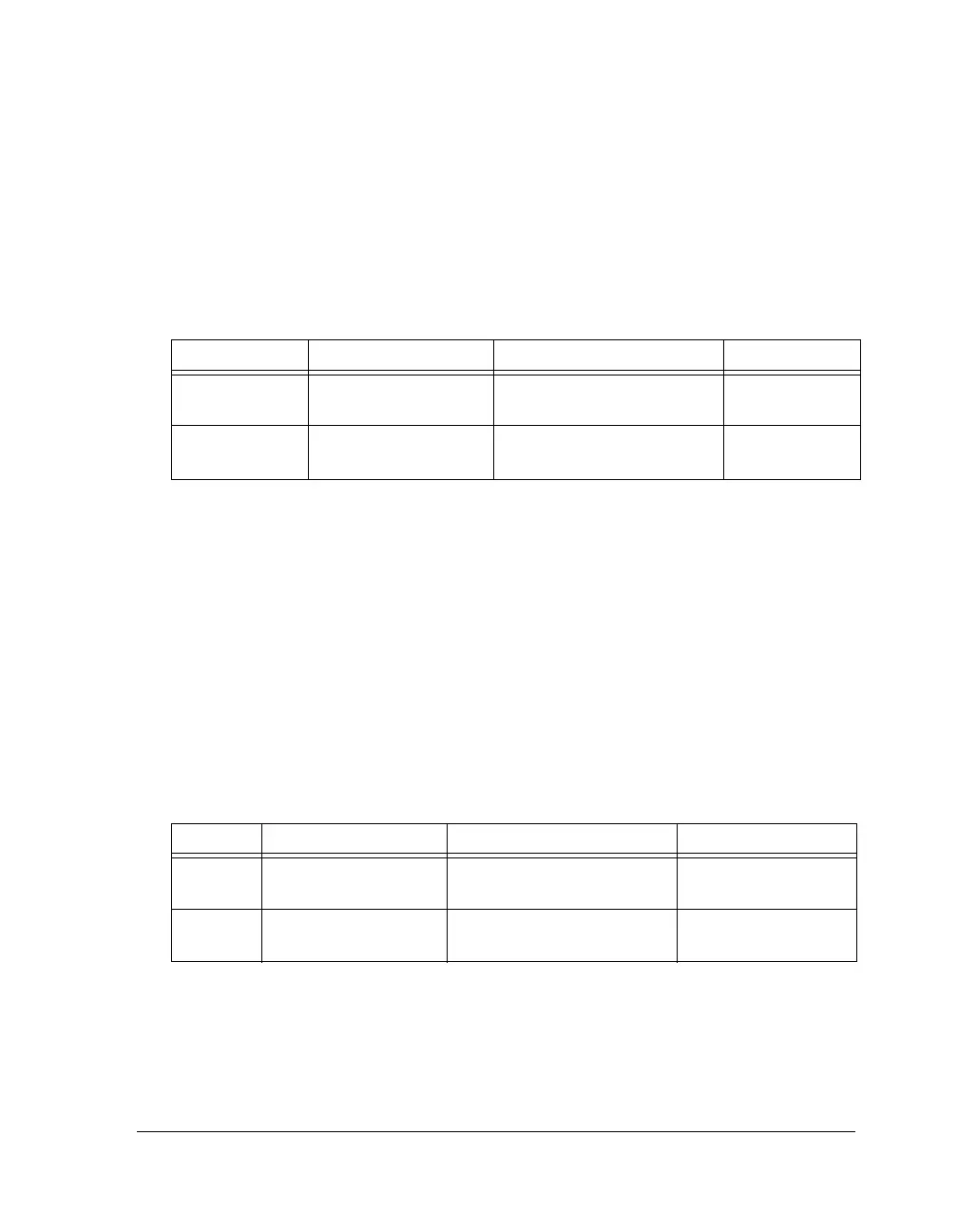

For a SIMD transfer, the controller can burst the 64-bit data given by the

core and writes it to N and N+1 memory locations. Since the burst length

is 4, SIMD mode transfers can be performed within one burst access.

The first access does the explicit 32-bit access (which results in the physi-

cal space in 2x16-bit words) while the 2nd 32-bit access dperforms the

implicit transfer. In total there is one read or write command per burst of

4x16-bit data as shown in Table 3-17.

Table 3-16. SDRAM SIMD Access

Access Logical x32 Physical x16 Comment

Explicit DM(0x200000) = R0 DM(0x400000) = R0(LSW);

DM(0x400001) = R0(MSW);

No Masking

Implicit DM(0x200001) = S0 DM(0x400002) = S0(LSW);

DM(0x400003) = S0(MSW);

No Masking

Table 3-17. DDR2 SIMD Burst Access

Access Logical x32 Physical x16 Comment

Explicit DM(0x200000) = R0 DM(0x400000) = R0(LSW);

DM(0x400001) = R0(MSW);

DDR2_DM1–0 = low

DDR2_DM1–0 = low

Implicit DM(0x200001) = S0 DM(0x400002) = S0(LSW);

DM(0x400003) = S0(MSW);

DDR2_DM1–0 = low

DDR2_DM1–0 = low

Loading...

Loading...