ADSP-214xx SHARC Processor Hardware Reference 15-1

15 SERIAL PERIPHERAL

INTERFACE PORTS

The ADSP-214xx processors are equipped with two synchronous serial

peripheral interface ports that are compatible with the industry-standard

serial peripheral interface (SPI). Each SPI port also has its own set of regis-

ters (the secondary register set contains a B as in SPIBAUDB). The SPI ports

support communication with a variety of peripheral devices including

codecs, data converters, sample rate converters, S/PDIF or AES/EBU digi-

tal audio transmitters and receivers, LCDs, shift registers,

microcontrollers, and FPGA devices with SPI emulation capabilities. The

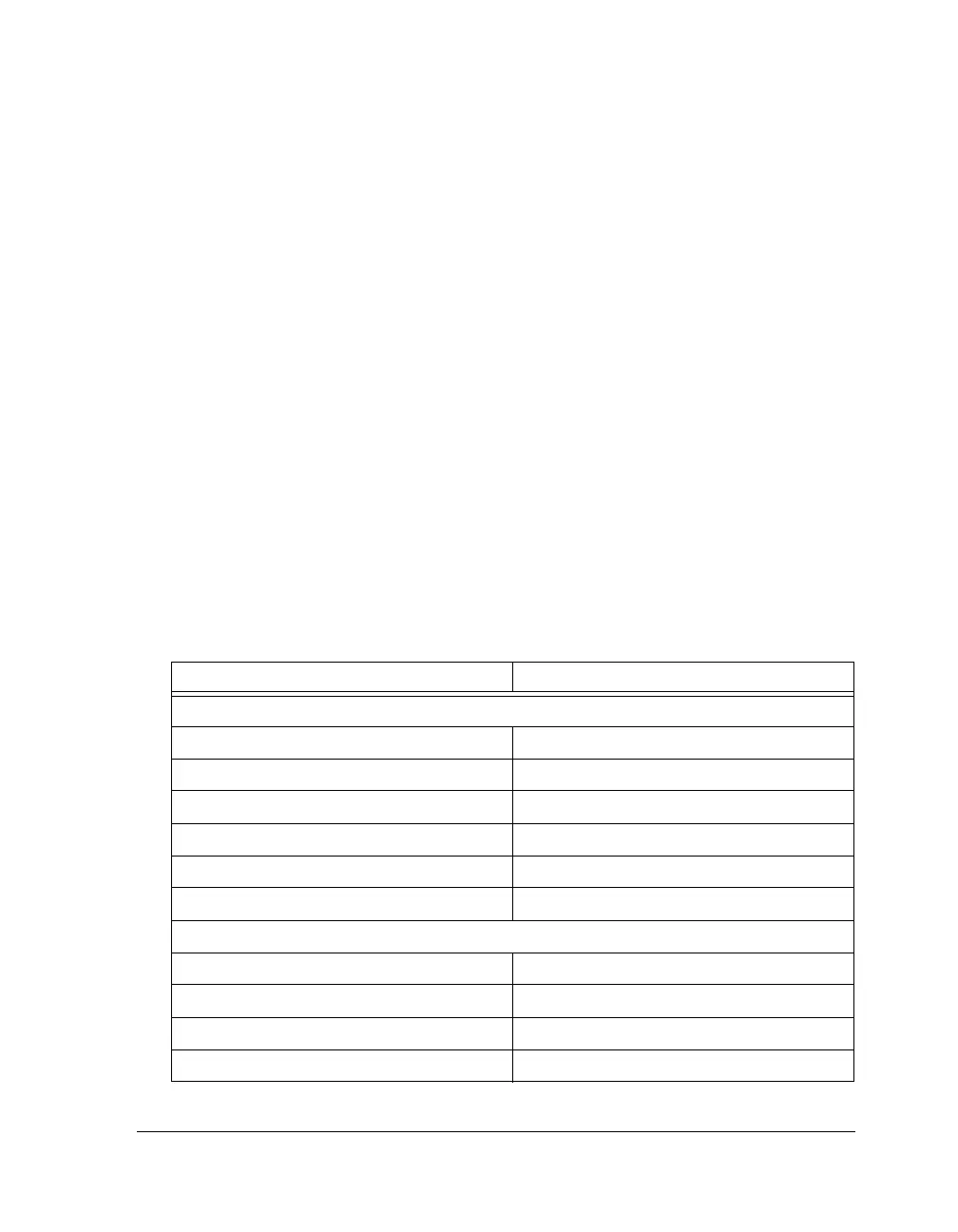

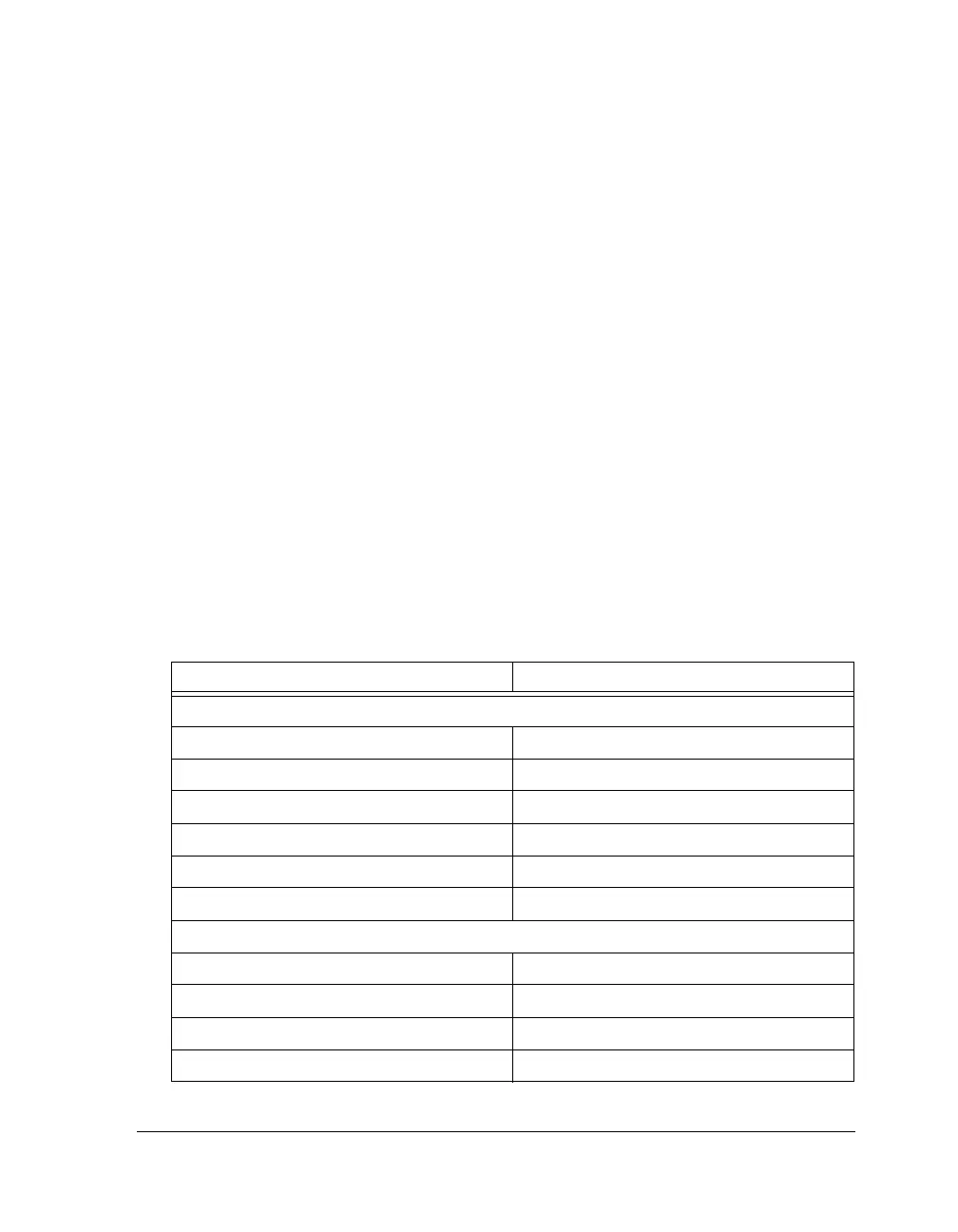

interface specifications are shown in Table 15-1.

Table 15-1. SPI Port Specifications

Feature SPI/SPIB

Connectivity

Multiplexed Pinout No

SRU DAI Required No

SRU DAI Default Routing N/A

SRU2 DPI Required Yes

SRU2 DPI Default Routing Yes

Interrupt Control Yes

Protocol

Master Capable Yes

Slave Capable Yes

Transmission Simplex Yes

Transmission Half Duplex Yes

Loading...

Loading...