Peripheral Registers

A-86 ADSP-214xx SHARC Processor Hardware Reference

FIR Debug Registers (FIRDEBUGCTL, FIRDBGADDR)

This register, shown in Figure A-39 and described in Table A-51, control

the debug operation of the FIR accelerator and should only be used in

debug mode.

11–7 CURCHNL Current Channel. Channel that is being processed in the

TDM slot. Zero indicates the last slot.

13–12 CURITER Current MAC Iteration. Current MAC iteration in multi

iteration mode. Zero indicates the final iteration.

31–14 Reserved

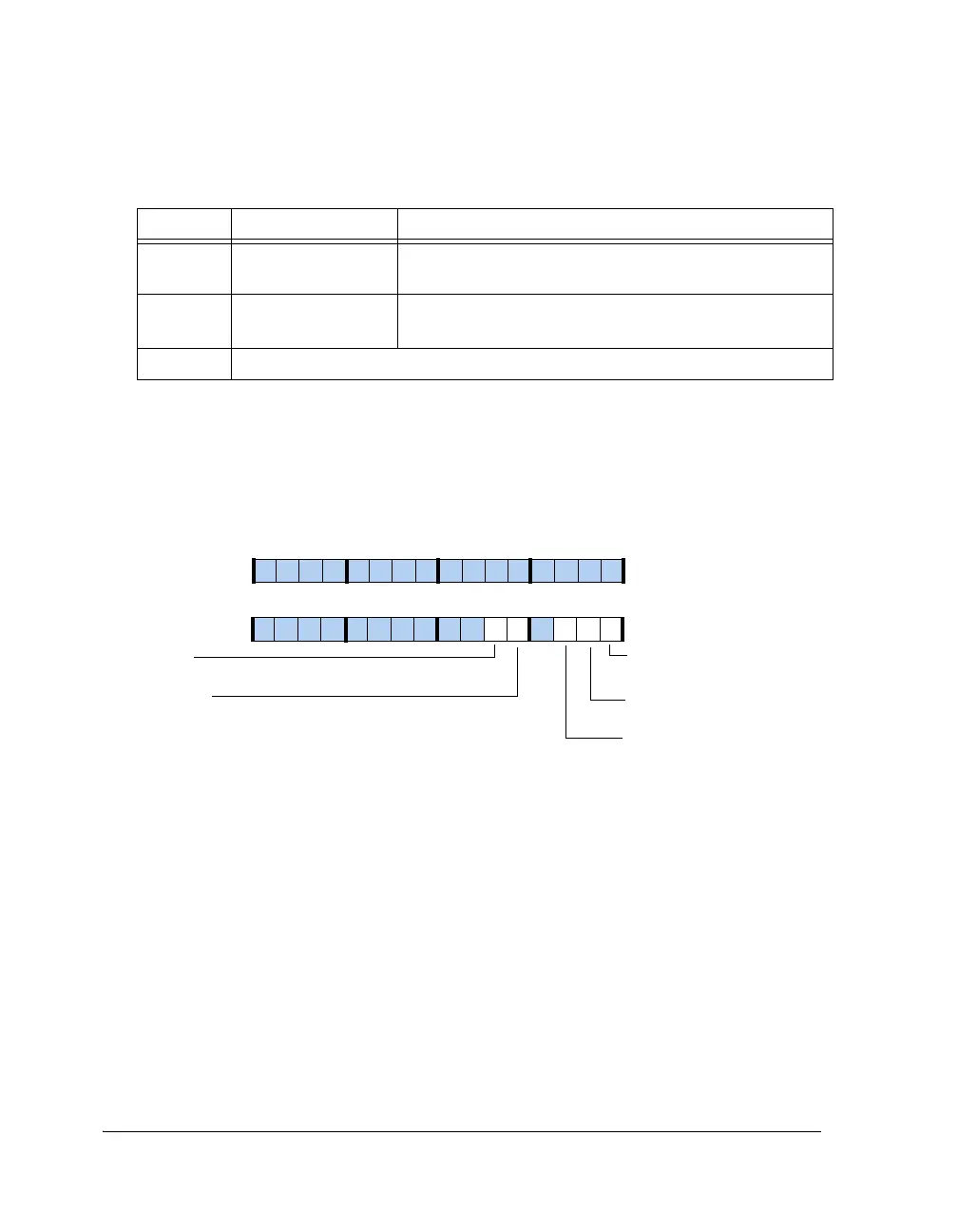

Figure A-39. FIRDEBUGCTL Register

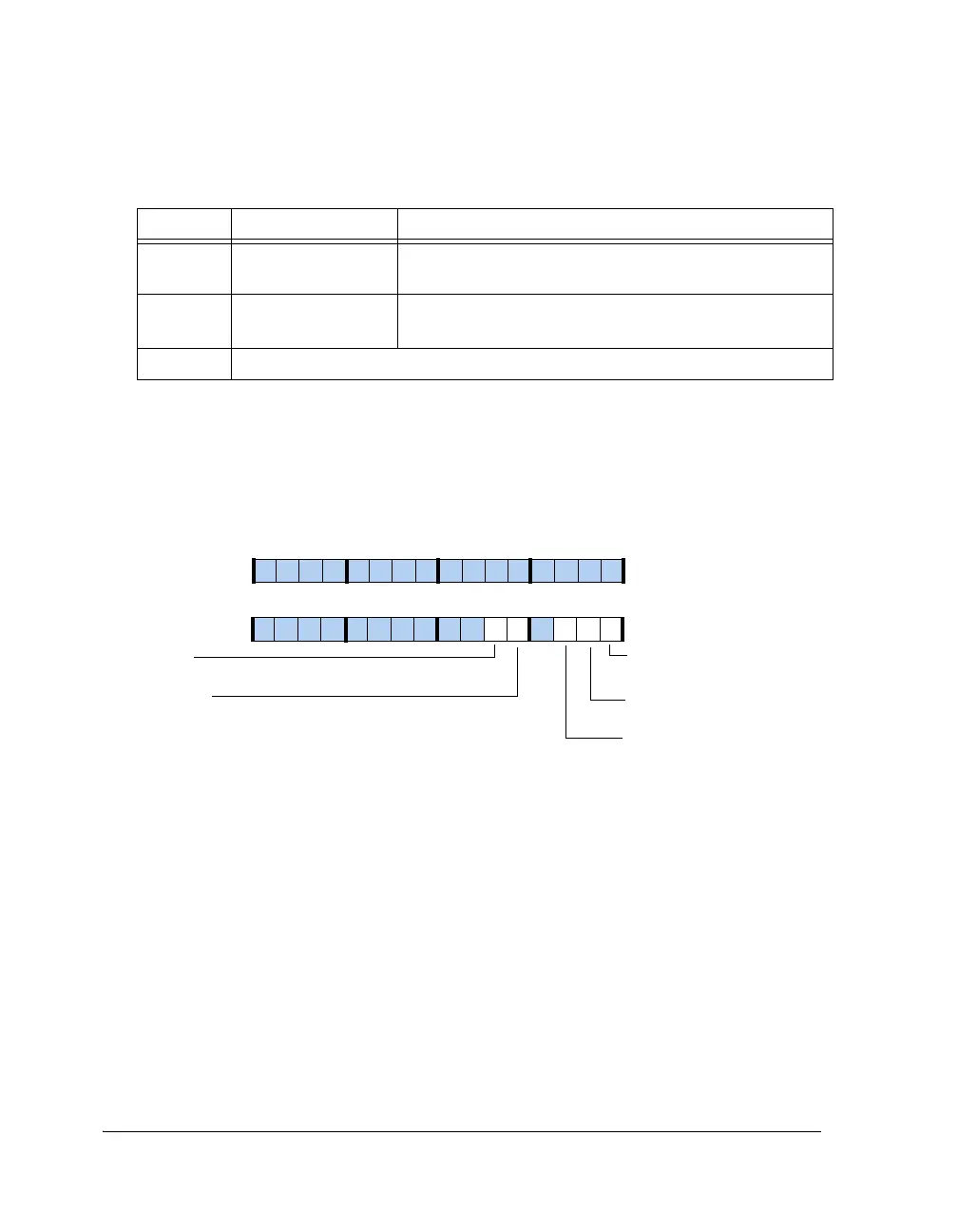

Table A-50. FIRDMASTAT Register Bit Descriptions (RO)

Bits Name Description

FIR_DBGMODE

FIR_ADRINC

Address Auto Increment

Debug Mode Enable

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

FIR_HLD

Hold or Single Step

FIR_DBGMEM

Local Memory Access

FIR_RUN

Release MAC

Loading...

Loading...