Operation Modes

10-28 ADSP-214xx SHARC Processor Hardware Reference

When

LAFS is set (=1), late frame syncs are configured. In this mode, the

first bit of the transmit data word is available (and the first bit of the

receive data word is latched) in the same serial clock cycle that the frame

sync is asserted. In multichannel operation, this is the case when frame

delay is zero. Receive data bits are latched by serial clock edges, but the

frame sync signal is checked only during the first bit of each word. Inter-

nally-generated frame syncs remain asserted for the entire length of the

data word in late framing mode. Externally-generated frame syncs are only

checked during the first bit. They do not need to be asserted after that

time period.

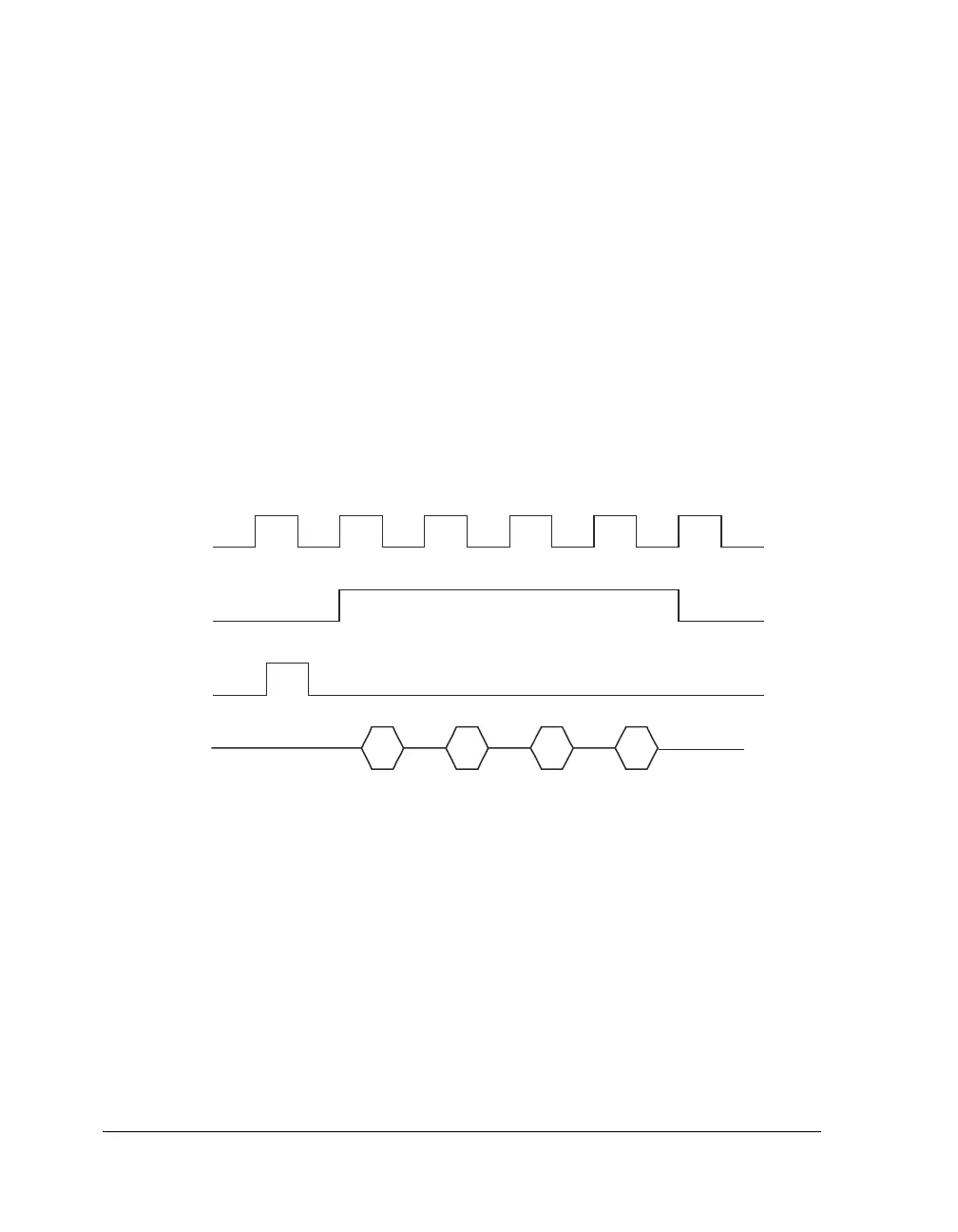

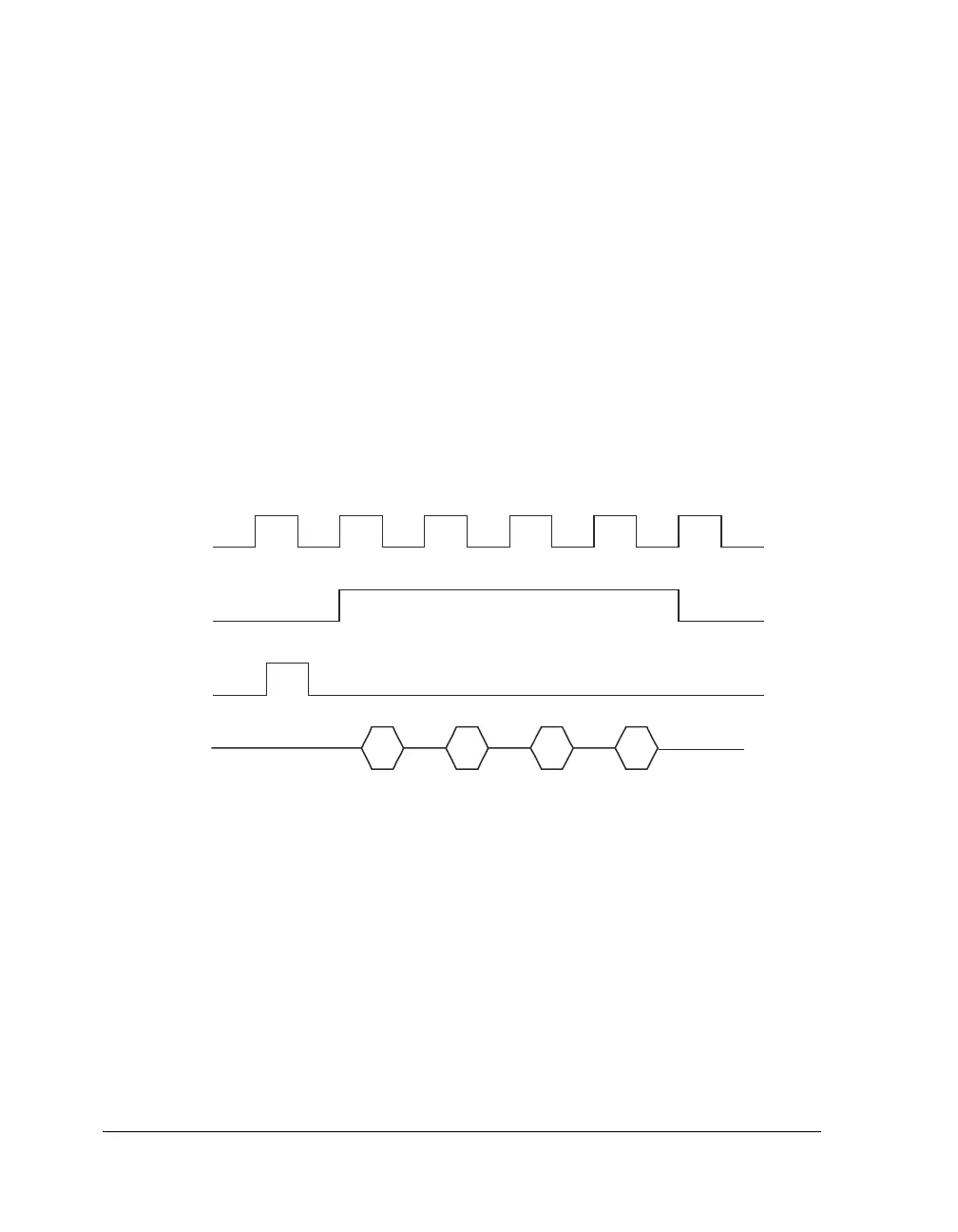

Figure 10-5 illustrates the two modes of frame signal timing.

Left-Justified Mode

Left-justified mode is a mode where in each frame sync cycle two samples

of data are transmitted/received—one sample on the high segment of the

frame sync, the other on the low segment of the frame sync.

Companding is not supported in left-justified or I

2

S mode.

Figure 10-5. Normal Versus Alternate Framing

B3 B2 B1 B0

...

SPORTX_CLK

LATE

FRAME

SYNC

DATA

EARLY

FRAME

SYNC

Loading...

Loading...