Peripherals Routed Through the DAI

A-182 ADSP-214xx SHARC Processor Hardware Reference

IDP Status Register (DAI_STAT0)

The IDP DMA status register shown in Figure A-97 and described in

Table A-94 reflects the status of the standard and ping-pong DMA

channels.

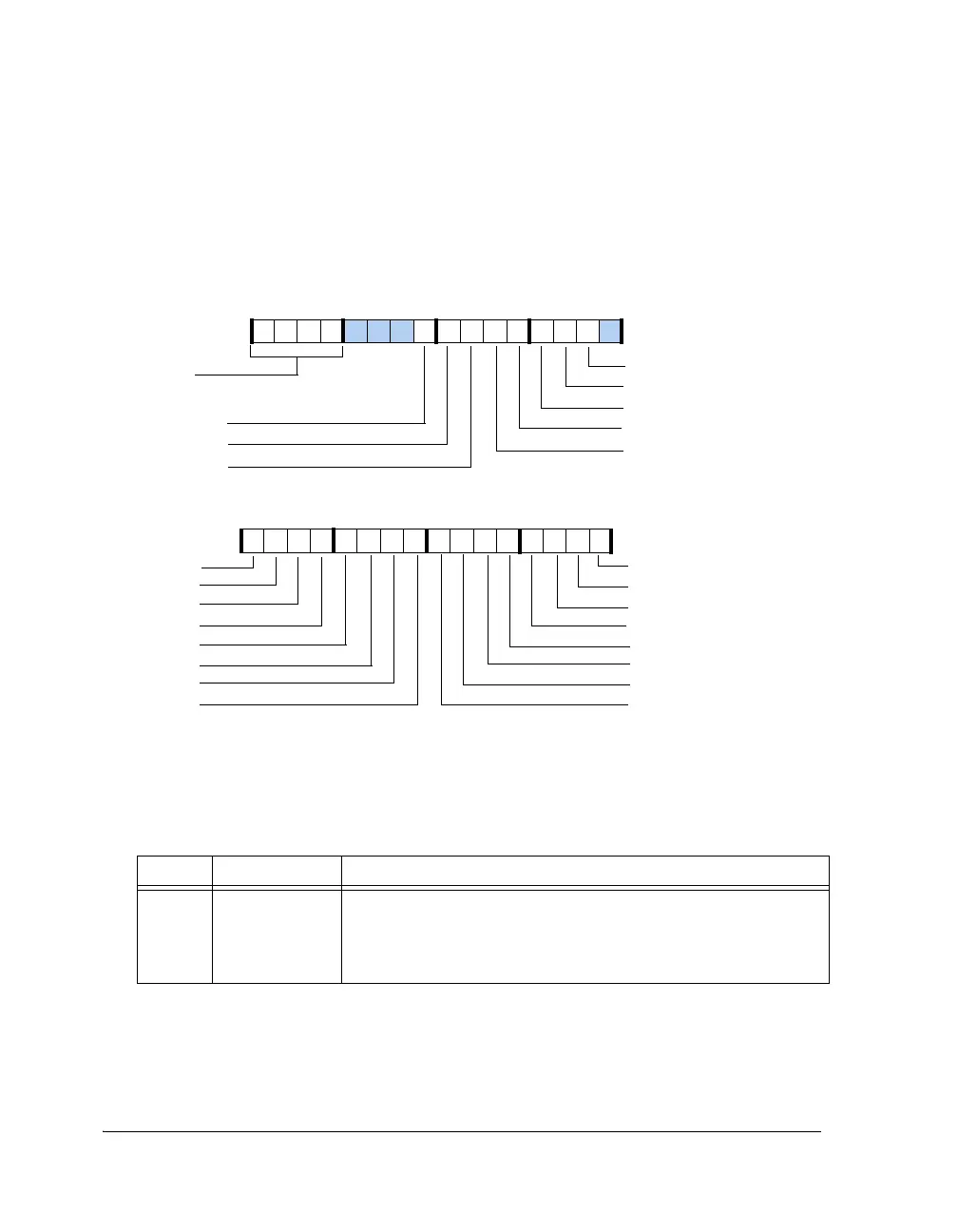

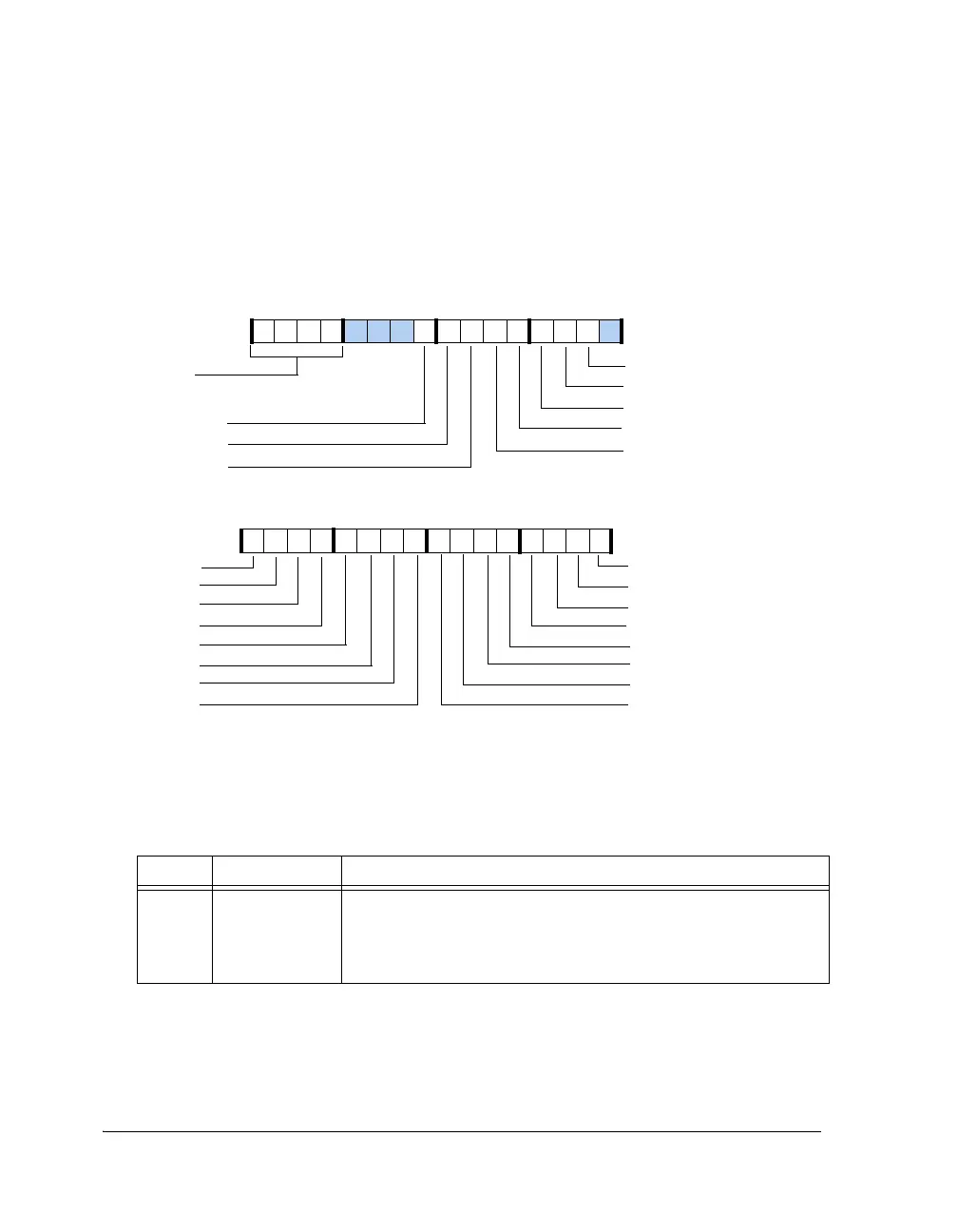

Figure A-97. DAI_STAT0 Register

Table A-94. DAI_STAT0 Register Bit Descriptions (RO)

Bit Name Description

7–0 SRU_PINGx_

STAT

Ping-Pong DMA Channel Status. Indicates the status of ping-pong

DMA in each respective channel (channel 7–0).

0 = DMA is not active

1 = DMA is active

IDP_FIFOSZ

Number of Valid Data in IDP FIFO

IDP_DMA7_STAT

IDP_DMA6_STAT

IDP_DMA3_STAT

IDP_DMA4_STAT

IDP_DMA1_STAT

IDP_DMA2_STAT

IDP_DMA0_STAT

IDP_DMA5_STAT

SRU_PING1_STAT

SRU_OVF0

SRU_PING0_STAT

SRU_PING2_STAT

SRU_PING3_STAT

SRU_PING4_STAT

SRU_PING5_STAT

SRU_PING6_STAT

SRU_PING7_STAT

SRU_OVF1

SRU_OVF2

SRU_OVF4

SRU_OVF7

SRU_OVF6

SRU_OVF5

SRU_OVF3

IDP Channel Overflow Ping-pong DMA

Channel Status

DMA Active Status for

IDP Channel

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...