ADSP-214xx SHARC Processor Hardware Reference A-181

Registers Reference

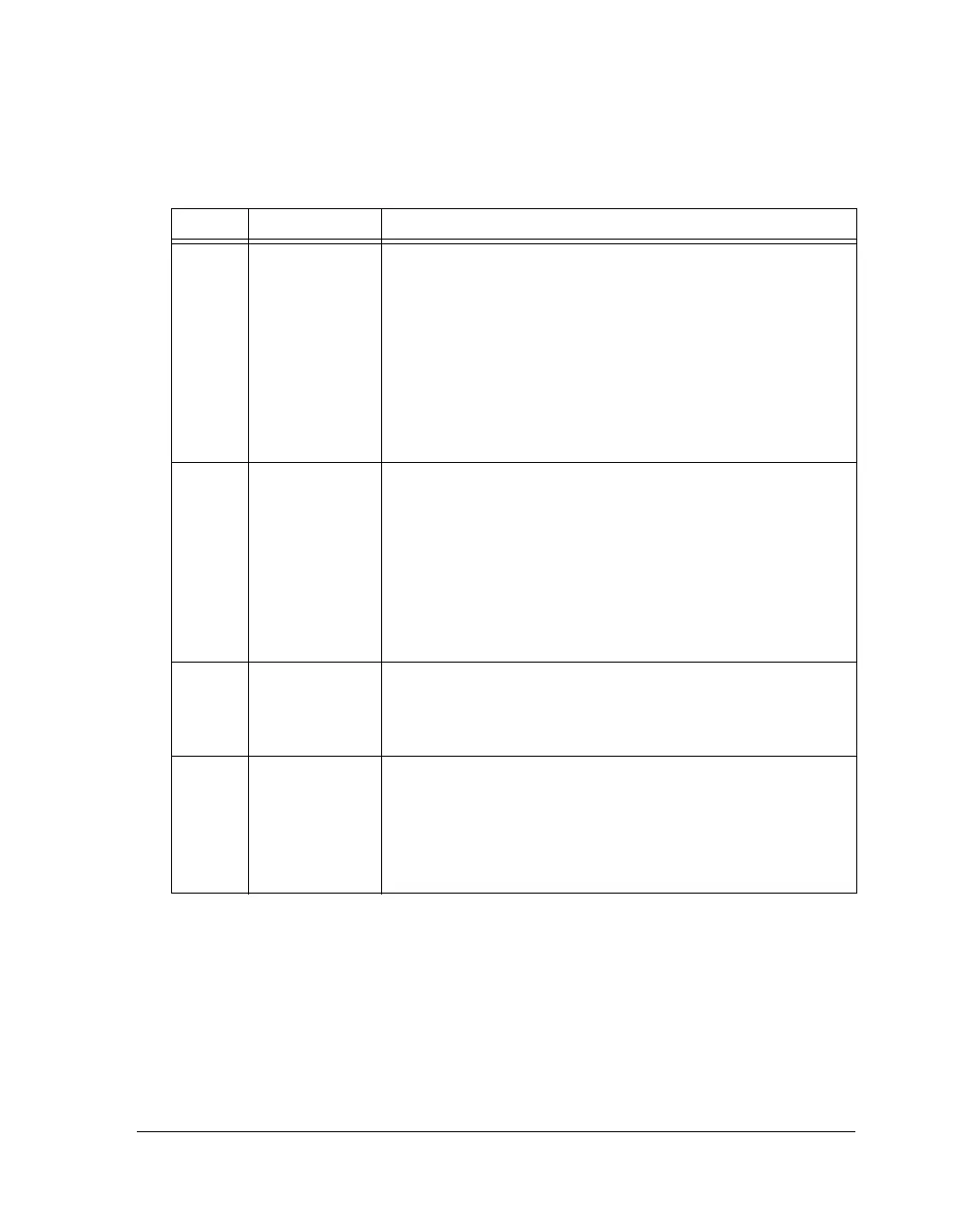

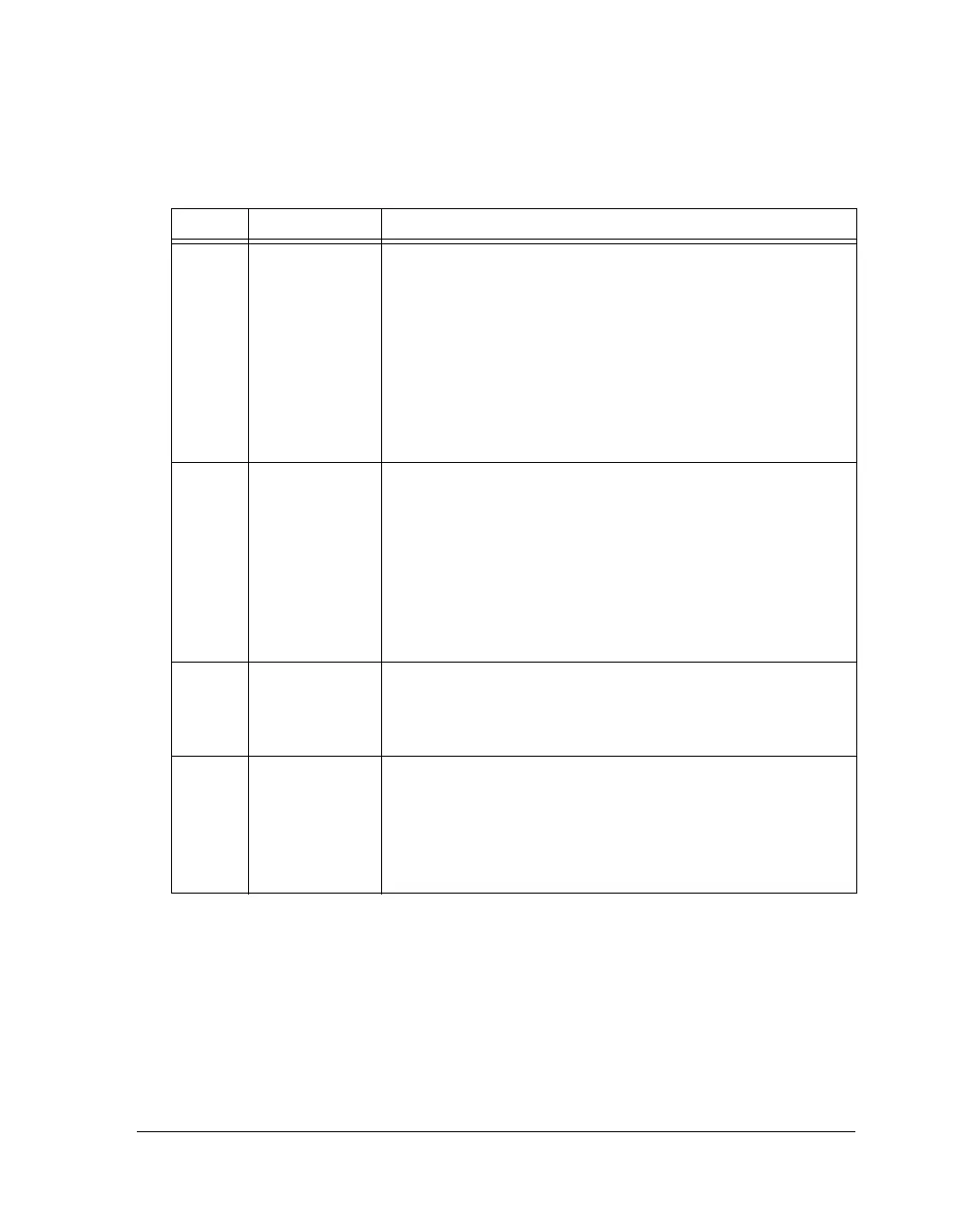

28–27 IDP_PDAP_

PACKING

Packing. Selects PDAP packing mode. These bits mask parallel sub

words from the 20 parallel input signals and packs them into a

32-bit word. The bit field indicates how data is packed. Selection

of packing mode is made based on the application.

00 = 8- to 32-bit (packing by 4)

01 = (11, 11, 10) to 32-bit (packing by 3)

10 = 16- to 32-bit (packing by 2)

11 = 20- to 32-bit (no packing). 12 LSBs are cleared

Note for input data width less than 20-bits, inputs are aligned to

MSB pins.

29 IDP_PDAP_

CLKEDGE

PDAP (Rising or Falling) Clock Edge.

Setting this bit (= 1) causes the data to latch on the falling edge

(PDAP_CLK_I signal). Clearing this bit (= 0) causes data to latch

on the rising edge (default).

Notice that in all four packing modes described, data is read on a

clock edge, but the specific edge used (rising or falling) is not indi-

cated.

0 = Data is latched on the rising edge

1 = Data is latched on the falling edge

30 (WO) IDP_PDAP_

RESET

PDAP Reset. A reset clears any data in the packing unit waiting to

get latched into the IDP FIFO. This bit reset the counter of the

PDAP and is useful for packing alignment. This bit always returns

a value of zero when read.

31 IDP_PDAP_

EN

PDAP Enable.

0 = Disconnects all PDAP inputs (data/control) from use as parallel

input channel

1 = Connects all PDAP inputs (data/control) from use as parallel

input channel. IDP channel 0 cannot be used as a serial input port

with this setting

Table A-93. IDP_PP_CTL Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...