Operating Modes

14-18 ADSP-214xx SHARC Processor Hardware Reference

Set the clock divisor and source and low-phase word first, followed by the

control register enable bits, which must be set together. When the

PCG_PW

register is set to zero (default) the FS pulse width is (divisor ÷ 2) for even

divisors and (divisor – 1) ÷ 2 for odd divisors. Alternatively, the PCG_PW

register could be set high for exactly one-half the period of CLKIN cycles for

a 50% duty cycle, provided the FS divisor is an even number.

Clock Configuration Examples

For a CLKIN = 33.330 MHz the two PCGs provide the three synchronous

clocks PCGx_CLK, SCLK and FS for the SRCs and external DAC. These divi-

sors are stored in 20-bit fields in the PCG_CTL registers.

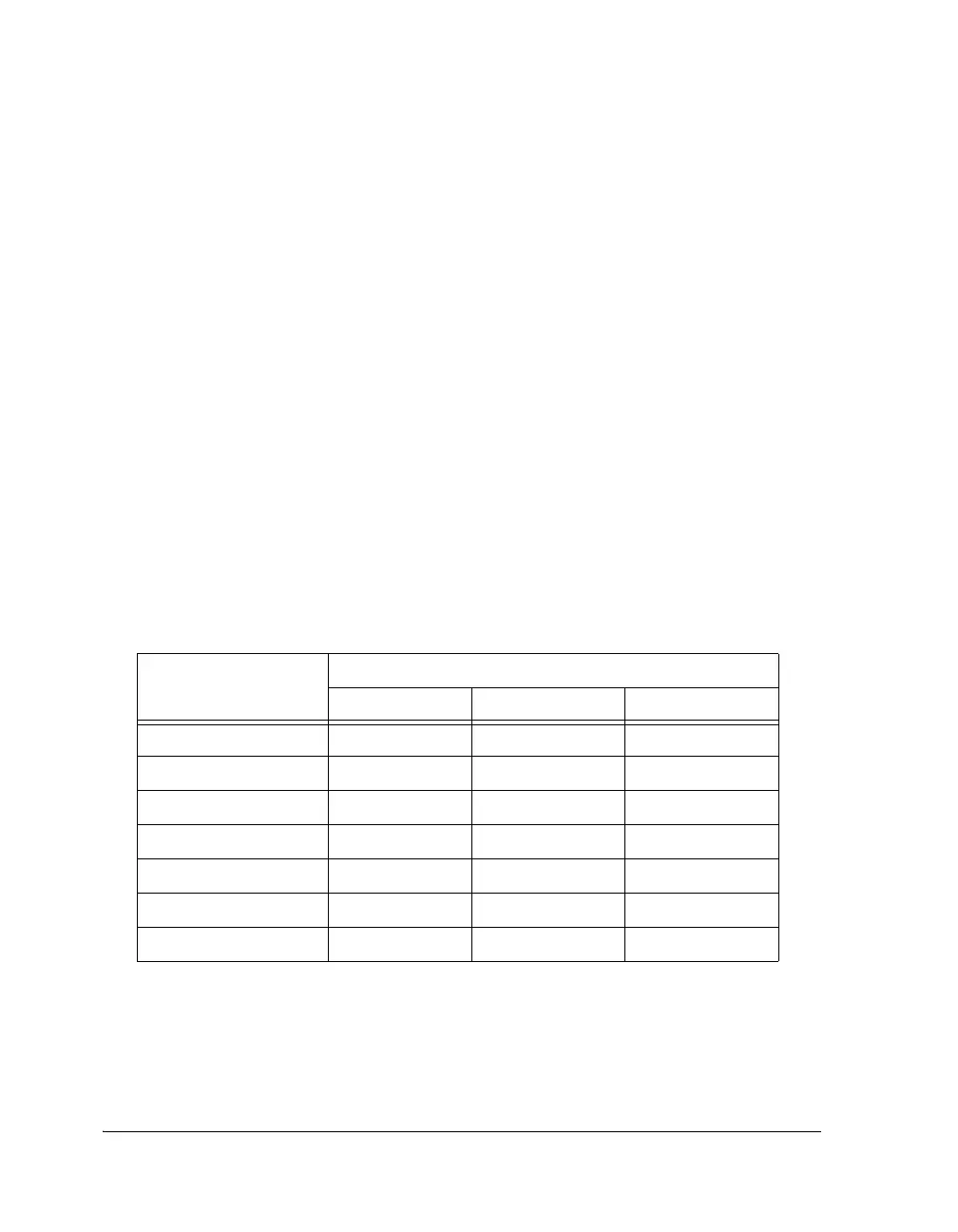

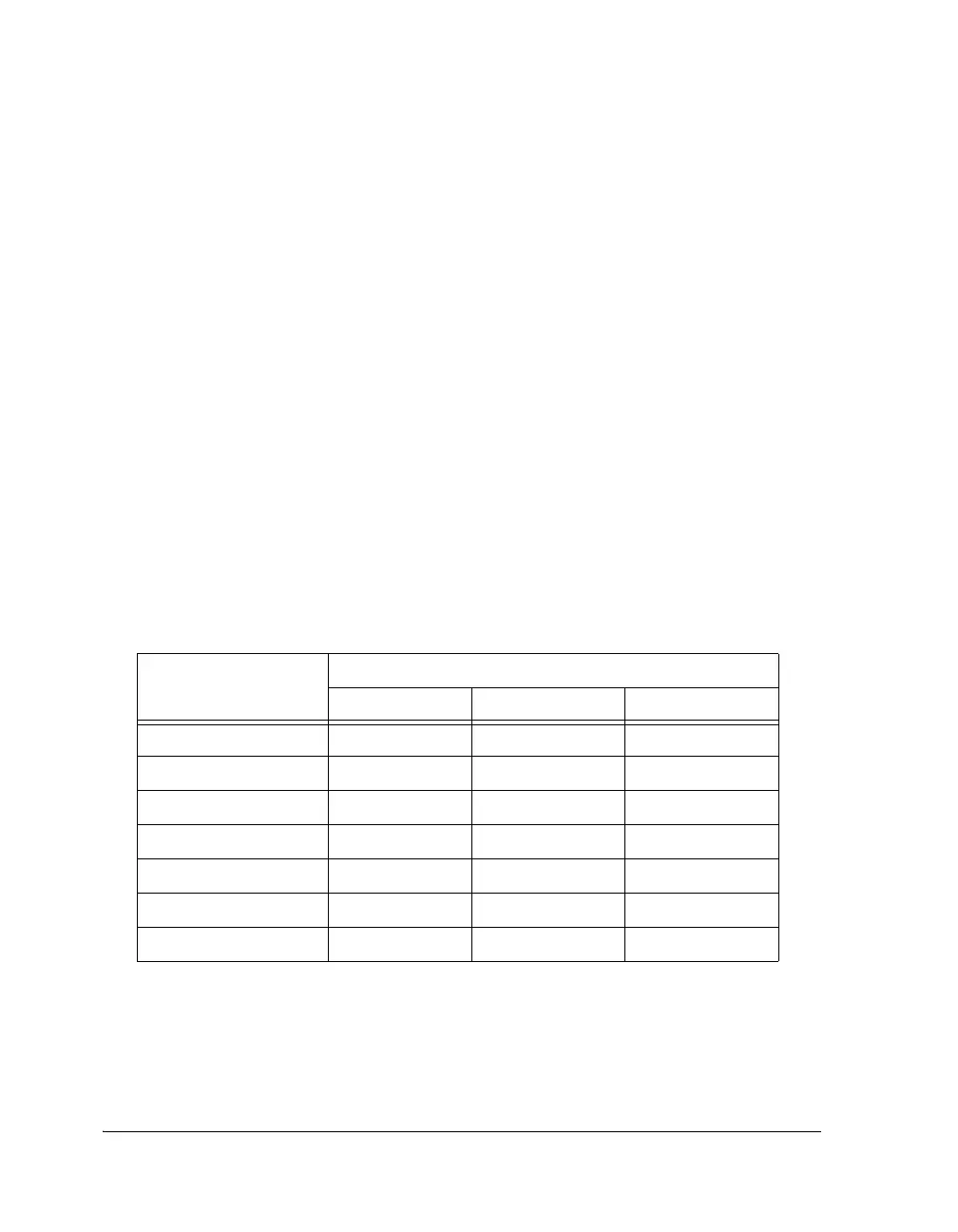

The integer divisors for several possible sample rates based on 33.330

MHz CLKIN are shown in Table 14-4.

Table 14-4. Precision Clock Generator Division Ratios

(33.330 CLKIN)

Sample Rate kHz)

PCG Divisors

CLKDIV B CLKDIV A FSDIV A

1

1 The frame sync divisor should be an even integer in order to produce a 50% duty cycle

waveform. See “Frame Sync” on page 14-7.

130.195 1 4 256

65.098 2 8 512

43.398 3 12 768

32.549 4 16 1024

26.039 5 20 1280

21.699 6 24 1536

18.599 7 28 1792

Loading...

Loading...