ADSP-214xx SHARC Processor Hardware Reference 14-17

Precision Clock Generator

The combined PCGs can provide a selection of synchronous clock fre-

quencies to support alternate sample rates for the ASRCs and external

DACs. However, the range of choices is limited by

CLKIN and the ratio of

PCG_CLKx_O:SCLK:FS which is normally fixed at 256:64:1 to support digital

audio left-justified, I

2

S and right-justified interface modes.

Many DACs also support 384, 512, and 786x FS for PCG_CLKx_O, which

allows some additional flexibility in choosing

CLKIN.

Note the falling edge of

SCLK must always be synchronous with both edges

of FS. This requires that the phase of the SCLK and FS signals for a com-

mon PCG (PCG A) be adjustable.

While the frequency of the master DAC clock (PCG_CLKx_O) must be syn-

chronous with the sample rate supplied to the external DAC, there is no

fixed phase requirement.

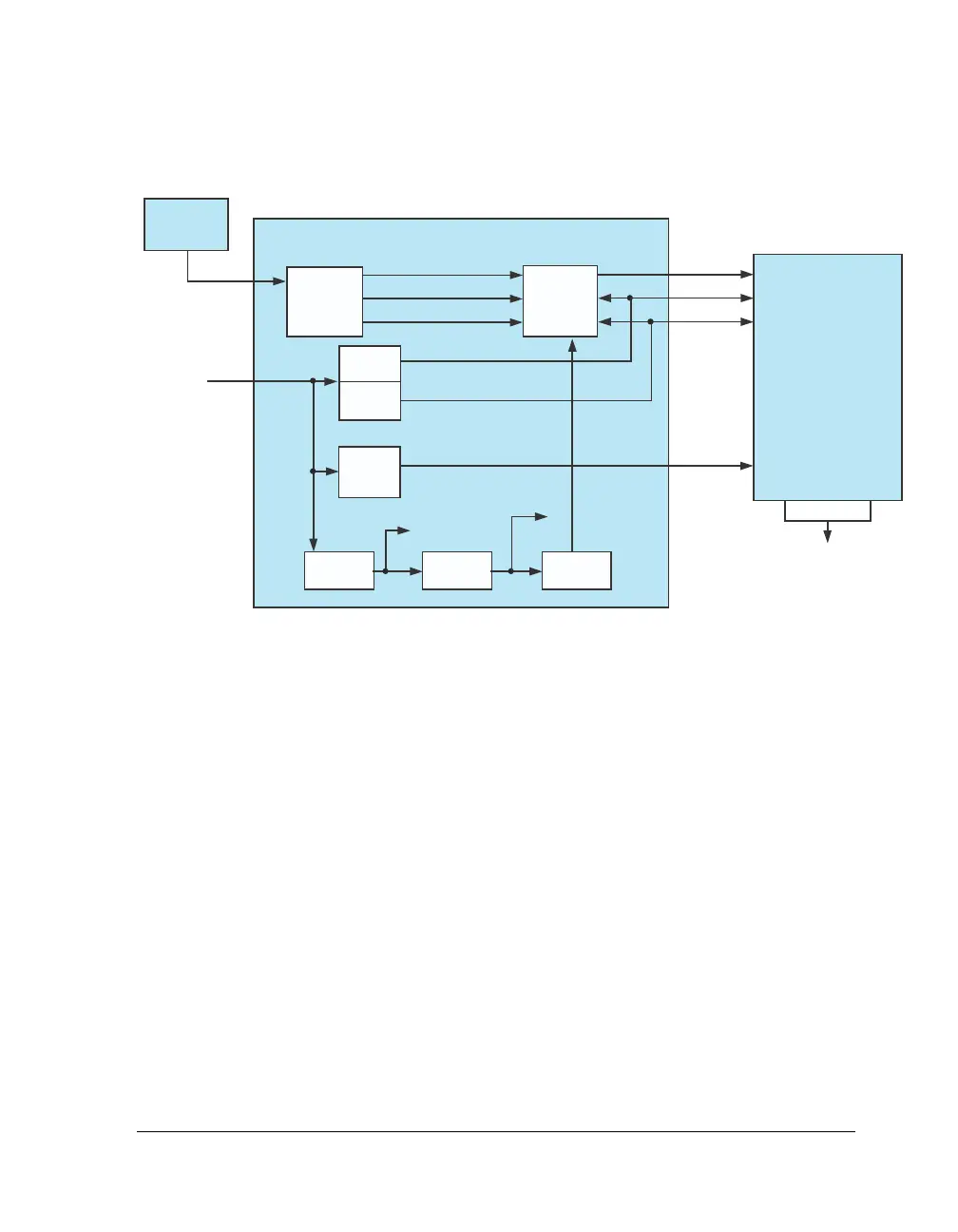

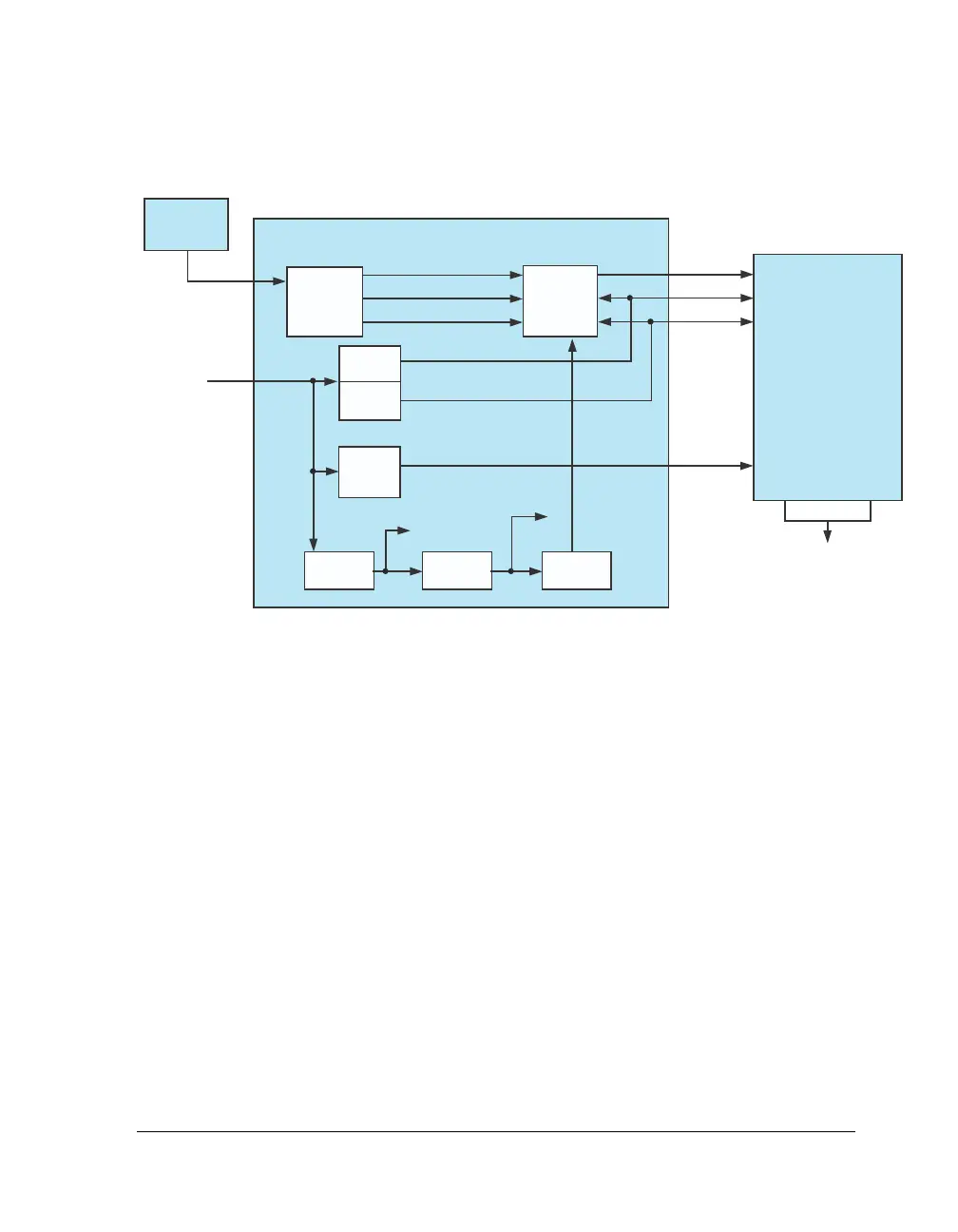

Figure 14-6. PCG Setup for I2S or Left-Justified DAI

ADSP-214xx

SPDIF

RX

ASRC

RxSCLK

RxLRCLK

SDATA

IN

PCG_

CLKA_O

PLL CCLK÷2 CCLK÷4

CCLK

PCLK

SDATA

OUT

DAI_P8

DAI_P9

DAI_P10

STEREO DAC

LEFT

OUT

RIGHT

OUT

MCLK

IN

DAI_P11

PCLK/4

FSYNC

A

(FS

OUT

)

SCLK

A

(64 FS

OUT

)

SCLKB

(256 FS

OUT

)

F

CLKIN

SPDIF

IN

(FS

IN

,44.1kHz)

DAI_P19

SDATA

IN

LRCLK

IN

SCLK

IN

FS

OUT

=65.1kHz

24-BIT

LEFT-JUSTIFIED

CD

PLAYER

HEAD PHONES

PCG_

CLKB_O

PCG_

FSA_O

Loading...

Loading...