ADSP-214xx SHARC Processor Hardware Reference 16-17

Peripheral Timers

Interrupts

This section describes all relevant registers and hardware to raise and ser-

vice interrupts.

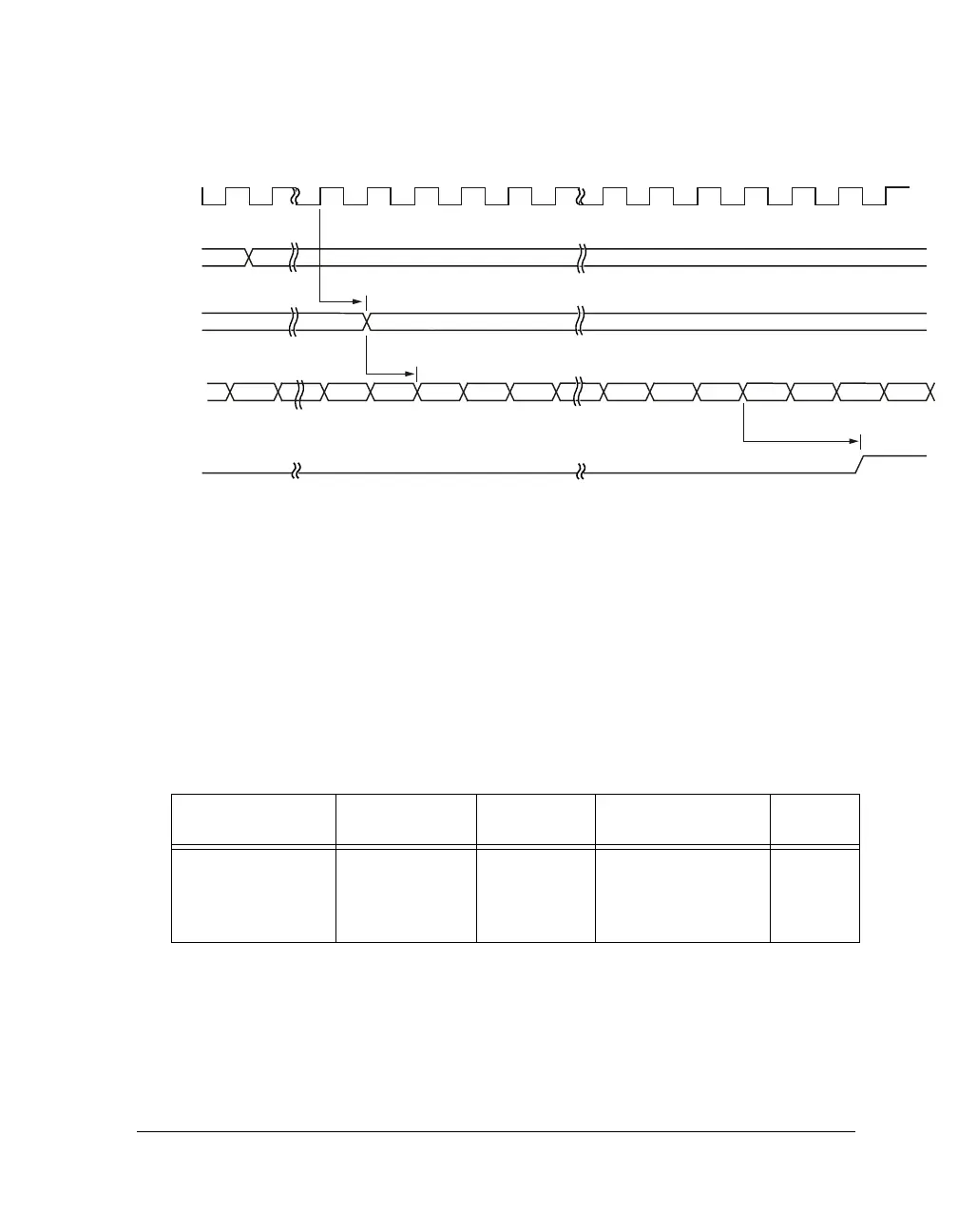

Table 16-5 provides an overview of timer interrupts.

Sources

Each timer generates a unique interrupt request signal. A common register

latches these interrupts so that a program can determine the interrupt

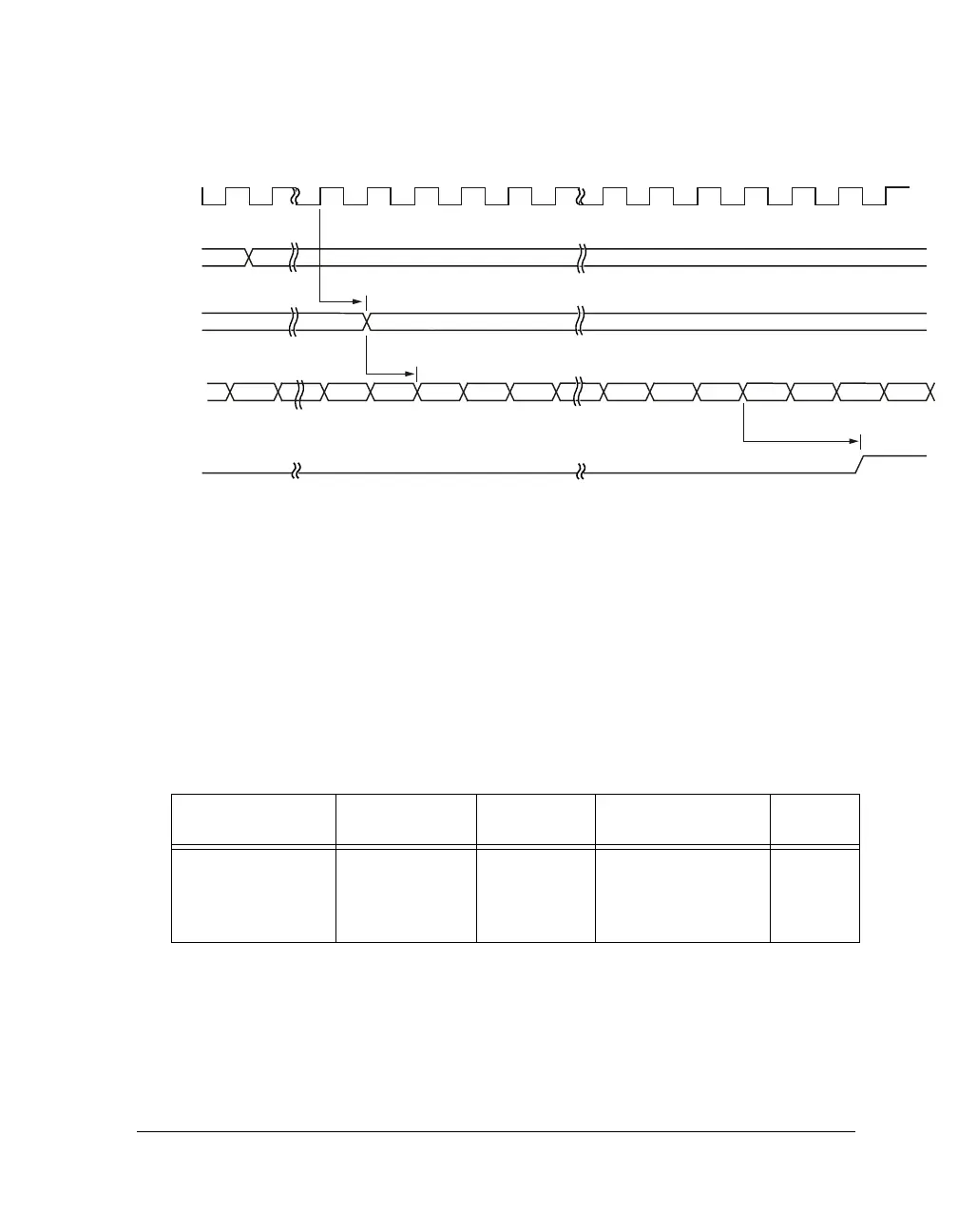

Figure 16-8. EXT_CLK Timing

Table 16-5. Timer Interrupt Overview

Interrupt Source Interrupt

Condition

Interrupt

Completion

Interrupt Acknowledge Default

IVT

GP Timer (PWM,

Width Capture, Ext

Watchdog, 2 chan-

nels)

– Timer expire

– Timer overflow

W1C (Write 1-to-clear)

TMxSTAT + RTI

instruction

P2I, P10I

TIMERx_I

P_BUF

PERIOD

IRQ

P

P

P

COUNTER

P - 2P - 1 1 02

cycle

cycle

P P - 2P - 1

sync delay

Loading...

Loading...