Operating Modes

2-42 ADSP-214xx SHARC Processor Hardware Reference

Peripheral DMA Bus

DMA-capable peripherals execute DMA data transfers to and from inter-

nal memory over the IOD0 bus. When more than one of these peripherals

requests access to the IOD0 bus in a clock cycle, the bus arbiter, which is

attached to the IOD0 bus, determines which master should have access to

the bus and grants the bus to that master.

IOP channel arbitration can be set to use either a fixed or rotating algo-

rithm by setting or clearing DCPR bit in the SYSCTL register as follows.

• (=0) fixed arbitration (default)

• (=1) rotating arbitration

IOD1 External Port Bus

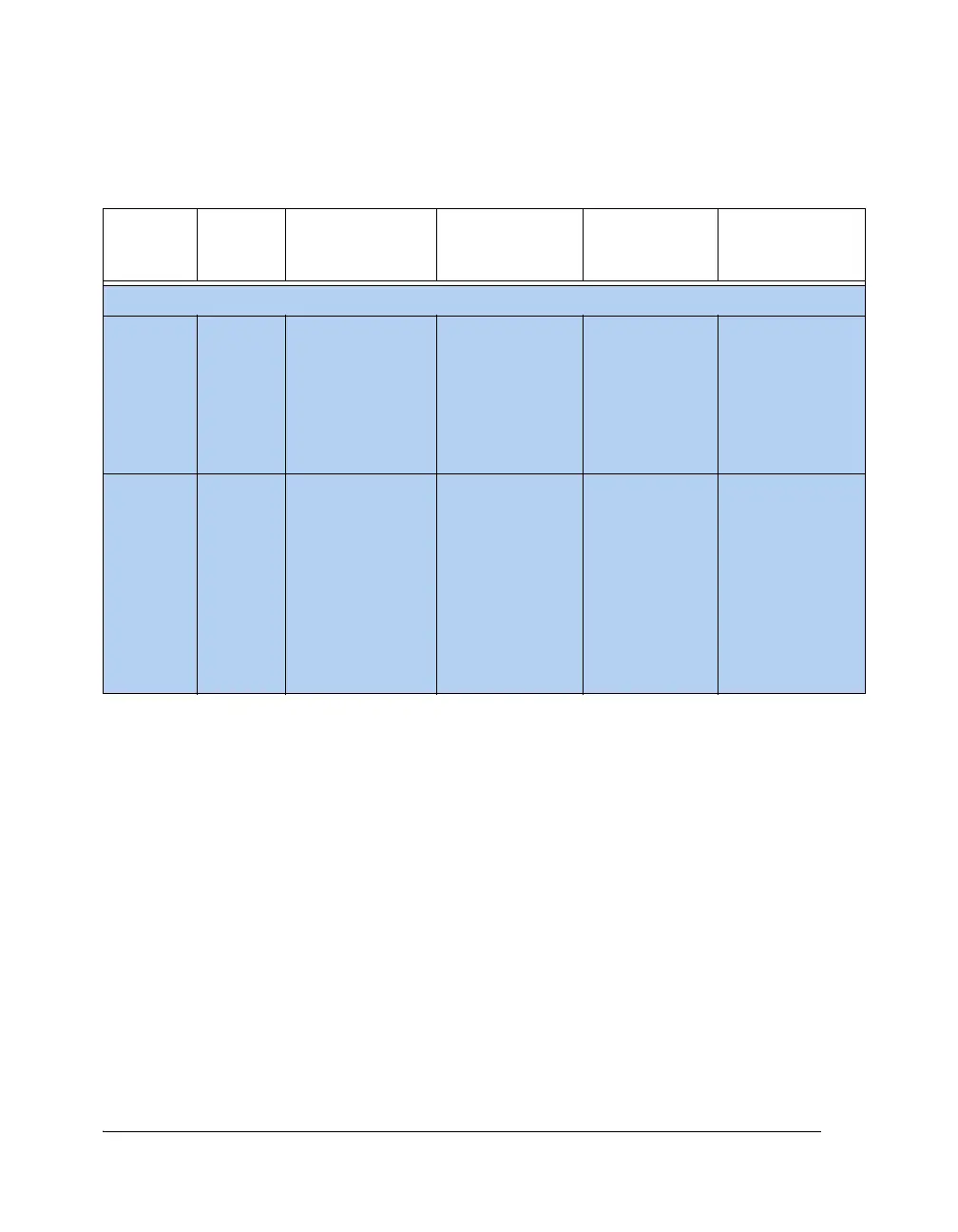

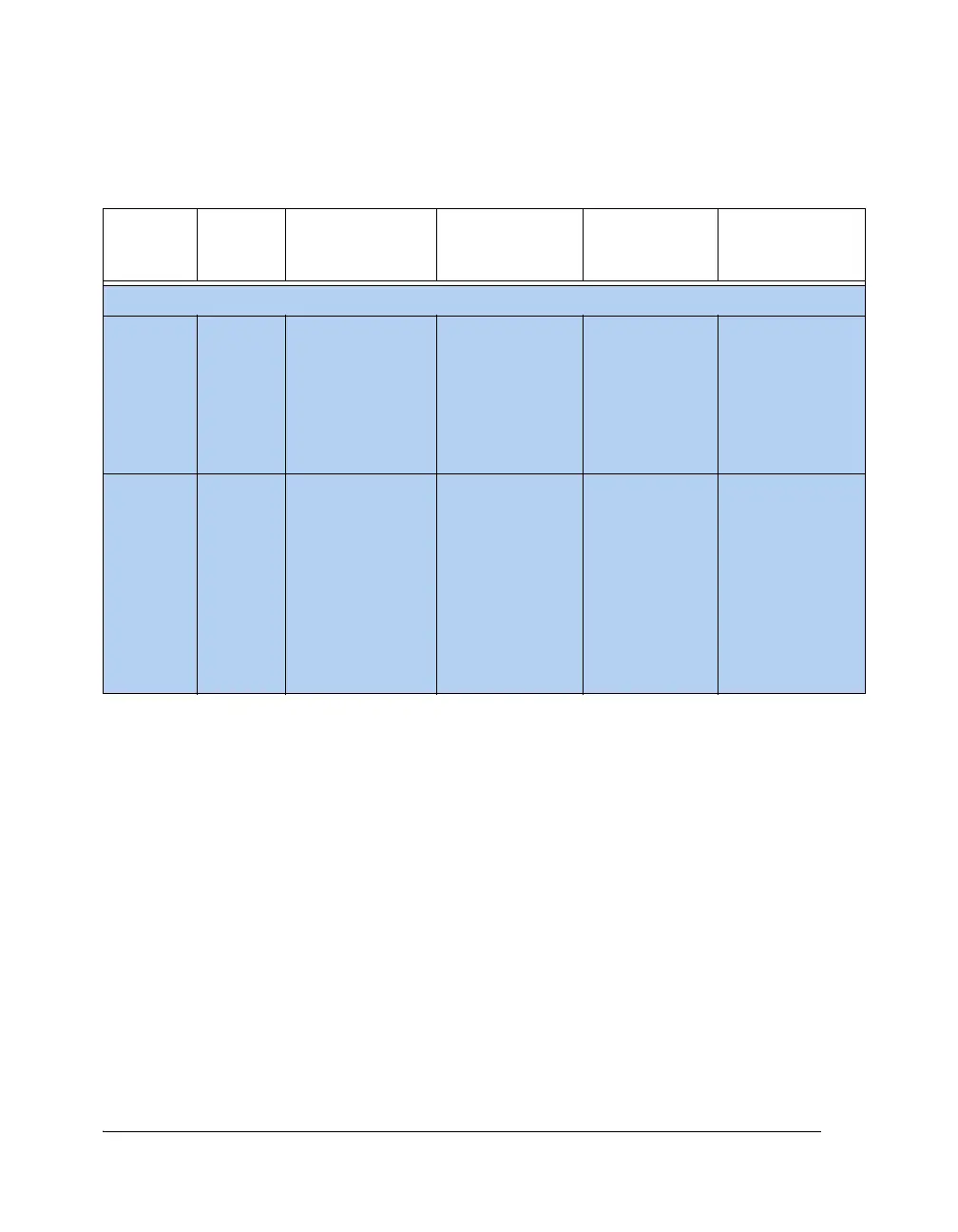

65 Q DMAC0 IIEP0, IMEP0,

ICEP0, EIEP0,

EMEP0 ELEP0,

EBEP0 RIEP0,

RCEP0 RMEP0,

EPTC0, EPTP0,

EPCP0

DFEP0

and

AMIRX

AMITX

(AMI only)

External Port

Memory DMA 0

66 R DMAC1 IIEP1, IMEP1,

ICEP1, EIEP1,

EMEP1 ELEP1,

EBEP1 RIEP1,

RCEP1 RMEP1,

EPTC1, EPTP1,

EPCP1

DFEP1

and

AMIRX

AMITX

(AMI only)

External Port

Memory DMA 1.

Note if the

DMAC0 channel

runs int-int mem-

ory and DMAC1

channel int-ext

memory, then

DMAC1 has higher

priority.

Table 2-28. DMA Channel 0–66 Priorities (Cont’d)

DMA

Channel

Number

Peripheral

Group

Control/Status

Registers

Parameter

Registers

Data Buffer Description

Loading...

Loading...